## AMERICAN UNIVERSITY OF BEIRUT

## TUNING THE CONTINUAL FLOW PIPELINE ARCHITECTURE

## by KOMAL MADAIAH JOTHI

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy to the Department of Electrical and Computer Engineering of the Faculty of Engineering and Architecture at the American University of Beirut

> Beirut, Lebanon February 2014

## AMERICAN UNIVERSITY OF BEIRUT

## TUNING THE CONTINUAL FLOW PIPELINE ARCHITECTURE

### by KOMAL MADAIAH JOTHI

Approved by:

Dr. Haitham Akkary, Associate Professor Electrical and Computer Engineering

Dr. Ayman Kayssi, Professor Electrical and Computer Engineering

Dr. Ali Chehab, Associate Professor Electrical and Computer Engineering

Dr Mazen Saghir, Associate Professor

Member of Committee Electrical and Computer Engineering, Texas A&M University at Qatar

Dr. Alga Alameldeen, Adjunct Faculty Me

Member of Committee Electrical and Computer Engineering, Portland State University

Date of dissertation defense: February 21, 2014

Advisor

Member of Committee

Member of Committee

## AMERICAN UNIVERSITY OF BEIRUT

## THESIS, DISSERTATION, PROJECT RELEASE FORM

| Student Name: | JOTHI | KOMAL            | MADAIAH               |     |

|---------------|-------|------------------|-----------------------|-----|

|               | Last  | First            | Middle                |     |

|               |       |                  |                       |     |

| OMaster's The | sis Ć | Master's Project | Ø Doctoral Dissertati | ion |

I authorize the American University of Beirut to: (a) reproduce hard or electronic copies of my thesis, dissertation, or project; (b) include such copies in the archives and digital repositories of the University; and (c) make freely available such copies to third parties for research or educational purposes.

I authorize the American University of Beirut, three years after the date of submitting my thesis, dissertation, or project, to: (a) reproduce hard or electronic copies of it; (b) include such copies in the archives and digital repositories of the University; and (c) make freely available such copies to third parties for research or educational purposes.

2014 MARCH 12 Date Signature

### ACKNOWLEDGMENTS

I would like to thank the Department of ECE and the then chair Dr. Karim Kabalan for giving me a chance to pursue my PhD at American University of Beirut. Thanks to the committee members, Dr. Ayman Kayssi, Dr. Ali Chehab, Dr. Mazen Saghir and Dr. Alaa Alameldeen for their feedback and comments.

Many thanks to Mageda Sharafeddine for the help with the power model. Also thanks to Saadallah Itani from the IT department for all the help with the servers. This work involved running a lot of simulations and the dedicated machines eased a lot of pressure. Thanks to Rabab Abi Shakra from the ECE Department and Lara Touma from the Dean's office for all the administrative help. Thanks to Nadine Knesevitch from the AUB library for her patience and help with formatting the final report.

Special thanks to my parents and family for their understanding and always being there for me.

These four years of my PhD were the happiest years of my life. I am very thankful to all my friends in Beirut for having made this such a memorable journey. Finally, I am most thankful to my advisor Dr. Haitham Akkary for what has been a thoroughly enjoyable ride.

V

## AN ABSTRACT OF THE DISSERTATION OF

<u>Komal Madaiah Jothi</u> for <u>Doctor of Philosophy</u> <u>Major:</u> Electrical and Computer Engineering

### Title: Tuning the Continual Flow Pipeline Architecture

One of the main factors that impacts performance of general purpose computer processors is misses to the data cache. Conventional techniques used in modern processors - building wide superscalars and large instruction buffers to hide the latency of these misses and keep the processor units busy - are not suitable for present and next generation processors that need to cater to high energy efficiency demands.

Continual Flow Pipeline (CFP) allows a processor core to handle hundreds of in-flight instructions without increasing cycle-critical pipeline resources. When a load misses the data cache, CFP checkpoints the processor register state and then moves all miss-dependent instructions into a low complexity waiting buffer to unblock the pipeline. Meanwhile, miss-independent instructions execute normally and update the processor state. When the miss data returns, CFP replays the miss-dependent instructions from the waiting buffer and then merges the miss dependent and independent execution results.

CFP was initially proposed for cache misses to DRAM. In that work, the missindependent and miss-dependent instructions execute at different times separated by a pipeline flush in between, based on the timing of the load miss event and the data arrival event.

In this thesis, we focus on reducing the execution overhead of CFP by avoiding the pipeline flush and executing dependent and independent instructions concurrently. The goal of these improvements is to gain performance by applying CFP to L1 data cache misses that hit the last level on-chip cache.

However, we see that when CFP is applied to L1 data cache misses, many applications or execution phases of applications incur excessive amount of replay and/or rollbacks to the checkpoint. This frequently cancels benefits from CFP and reduces performance.

We mitigate this issue by using a novel virtual register renaming substrate, and by tuning the replay policies to eliminate excessive replays and rollbacks to the checkpoint. We describe these new design optimizations and show, using Spec 2006 benchmarks and microarchitecture performance and power models of our design, that our Tuned-CFP architecture improves performance and energy consumption over previous CFP architectures by ~10% and ~8%, respectively. We also demonstrate that our proposed architecture gives better performance return on energy per instruction compared to a conventional superscalar as well as previous CFP architectures.

# CONTENTS

| ACKNOWLEDGMENTSV                                                             |

|------------------------------------------------------------------------------|

| ABSTRACTVI                                                                   |

| LIST OF ILLUSTRATIONS XIII                                                   |

| LIST OF TABLESXV                                                             |

| Chapter                                                                      |

| 1. INTRODUCTION1                                                             |

| 1.1 Motivation1                                                              |

| 1.2. Dissertation Contribution                                               |

| 1.3 Dissertation Related Publications10                                      |

| 1.4 Document Organization11                                                  |

| 2. BACKGROUND WORK                                                           |

| <ul> <li>2.1 Conventional Mechanisms Used in Commercial Processors</li></ul> |

| 2.2 Mechanisms in Literature                                                 |

| 2.2.1 Runahead Execution Processors                                  | 20 |

|----------------------------------------------------------------------|----|

| 2.2.2 Waiting Instruction Buffer                                     | 23 |

| 2.2.3 Continual Flow Pipelines                                       | 25 |

| 2.2.3.1 Register Management in CFP                                   | 25 |

| 2.2.3.2 Slice Buffer Management in CFP                               | 26 |

| 2.2.3.3 Load and Store Management in CFP                             | 27 |

| 2.2.3.4 CFP on In-order Processors                                   | 29 |

| 2.2.3.5 Limitations of Conventional-CFP                              | 29 |

| 2.2.4 Kilo Instruction Processors                                    | 33 |

| 2.2.5 Flea-Flicker                                                   | 34 |

| 2.2.6 iCFP and BOLT                                                  | 34 |

| 2.2.7 Sun Microsystems ROCK                                          | 35 |

| 2.3 Simultaneous Multithreading                                      | 35 |

| 2.4 Architectures with Virtual Register Renaming                     | 37 |

| 2.4.1 Virtual Registers                                              | 37 |

| 2.4.2 Virtual Register Renaming                                      | 37 |

| 2.5 Summary                                                          | 39 |

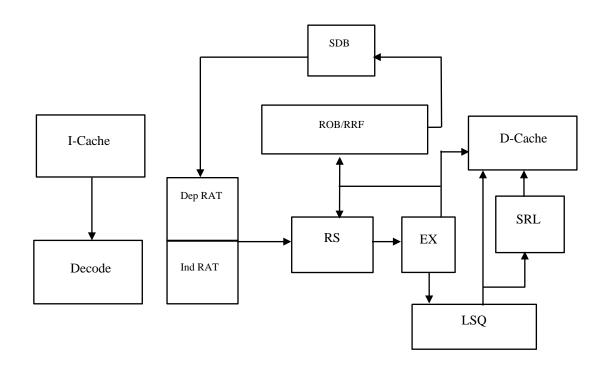

| 3. SIMULTANEOUS-CFP ARCHITECTURE                                     | 40 |

| 3.1 Simultaneous-CFP Microarchitecture                               | 40 |

| 3.1.1 Microarchitecture Overview                                     | 40 |

| 3.1.2 Independent Thread Execution and Dependent Thread Construction | 44 |

| 3.1.3 Dependent Thread Execution                                     | 45 |

| 3.1.4 Checkpoints and Results Integration                            | 46 |

| 3.1.5 Memory Ordering and Load Store Execution                       | 47 |

| 3.1.6 Resource Sharing During Simultaneous Execution                 | 48 |

| 3.2 Limitations of S-CFP                                             | 48 |

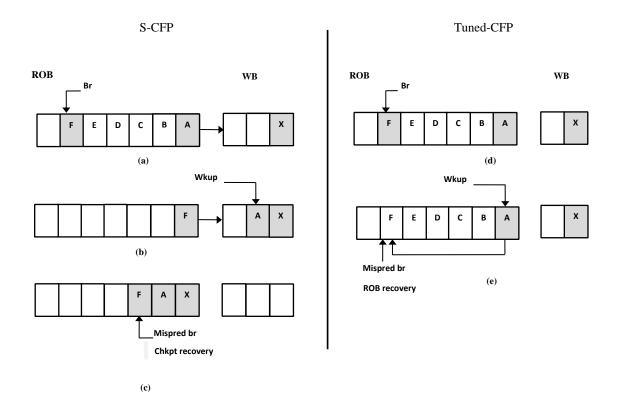

| 3.2.1 Unoptimized S-CFP Execution Examples                           | 49 |

| 3.2.2 Tuned-CFP Execution Examples                                   | 53 |

| 3.3 Limit Studies to Quantify the Limitations of S-CFP             | 54 |

|--------------------------------------------------------------------|----|

| 3.3.1 Buffer Full Condition                                        | 55 |

| 3.3.2 Miss-dependent Branch Mis-predictions                        | 55 |

| 3.3.3 Unnecessary Replay Overhead                                  | 57 |

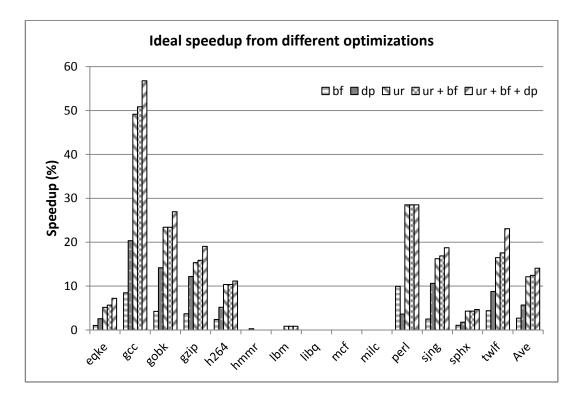

| 3.3.4 Combining Limit Studies                                      | 57 |

| 4. TUNED-CFP ARCHITECTURE                                          | 59 |

| 4.1 Tuned-CFP Microarchitecture                                    | 59 |

| 4.1.1 Tuned-CFP Microarchitecture Overview                         | 59 |

| 4.1.2 Miss-independents Execution                                  | 60 |

| 4.1.3 Replay Loop and Miss-dependents Execution                    | 61 |

| 4.1.4 Reservation Stations                                         | 63 |

| 4.1.5 Waiting Buffer                                               | 64 |

| 4.1.6 Register File and Results Integration                        | 65 |

| 4.1.7 Load and Store Execution                                     | 66 |

| 4.1.8 Miss-dependent Branch Predictor                              | 66 |

| 5. MEMORY ORDERING MECHANISMS                                      | 68 |

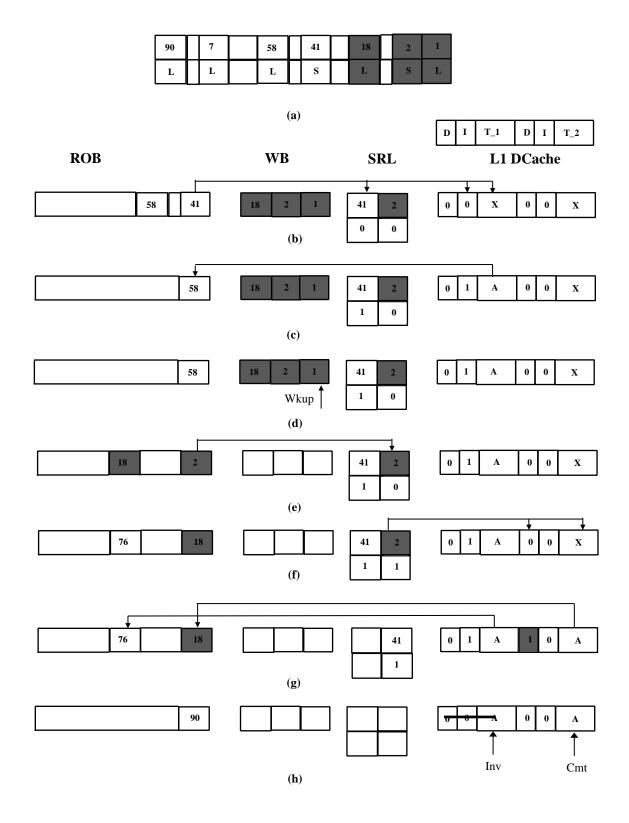

| 5.1 Architecture Support for Speculative Cache and SRL Mechanism . | 68 |

| 5.1.1 L1 Data Cache State                                          | 69 |

| 5.1.2 Independent Thread Store Execution                           | 69 |

| 5.1.3 Dependent Thread Store Execution                             | 70 |

| 5.1.4 Independent Thread Load Execution                            | 70 |

| 5.1.5 Dependent Thread Load Execution                              |    |

| 5.1.6 Recovering from Memory Dependence Mis-predictions            | 71 |

| 5.1.7 Victim Cache                                                 | 72 |

| 5.2 Working of Speculative Cache with an Execution Sequence        |    |

| 5.3 Synchronization of Loads and Stores                            | 77 |

| 5.4 Memory Ordering Design Choices                                 | 79 |

| XPER  | IMENTAL RESULTS                                                                          |

|-------|------------------------------------------------------------------------------------------|

| 7.1 A | Analysis of Energy Characteristics of Non-CFP Superscalar Cores                          |

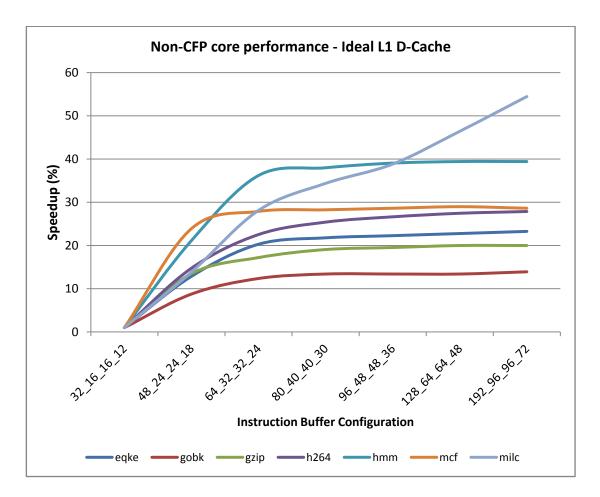

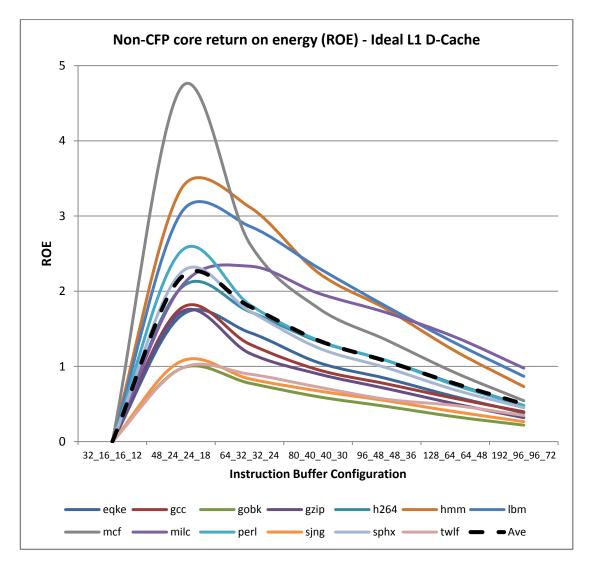

|       | 7.1.1 Energy Characteristics of 4-wide Non-CFP Superscalar<br>Core with Ideal Data Cache |

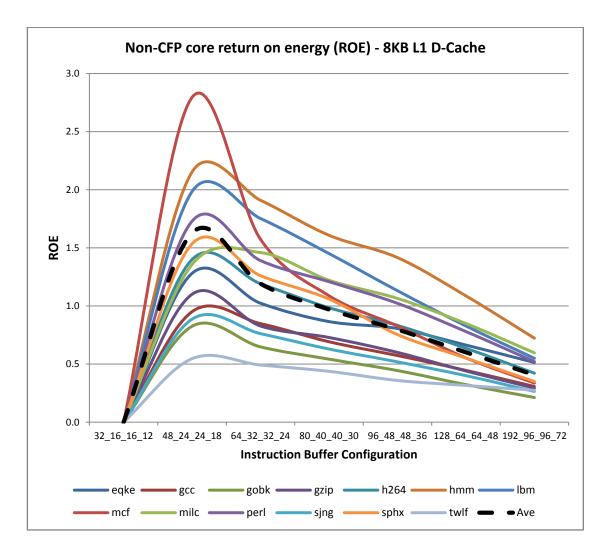

|       | 7.1.2 Selecting the L1 Data Cache Size                                                   |

|       | 7.1.3 Varying Instruction Buffer Sizes with Optimal L1 Data Cache                        |

| 7.2 E | valuating Performance                                                                    |

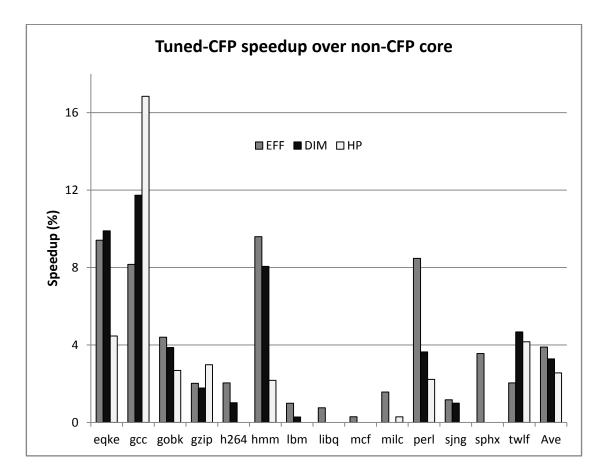

|       | 7.2.1 Comparing Tuned-CFP to Non-CFP Core Architectures                                  |

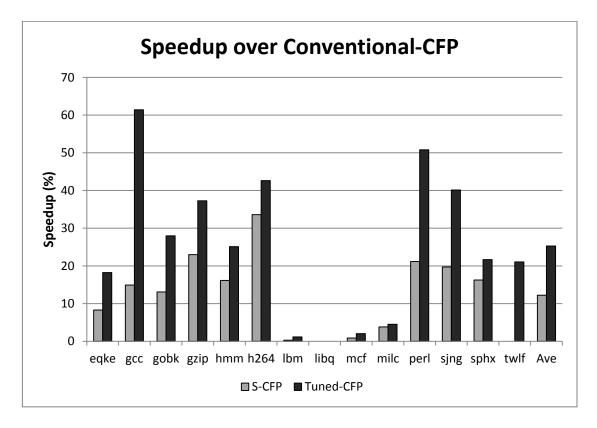

|       | 7.2.2 Comparing Tuned-CFP and Simultaneous-CFP to Conventional-CFP                       |

|       | 7.2.3 Comparing Tuned-CFP to Simultaneous-CFP                                            |

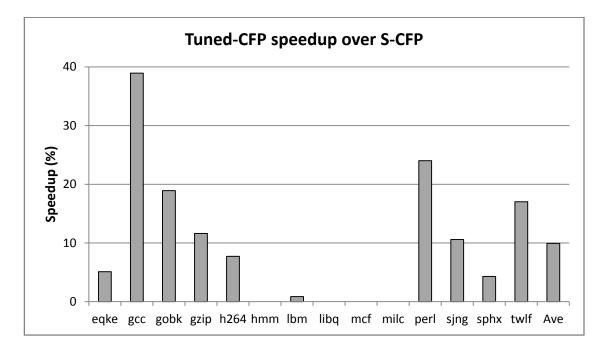

|       | 7.2.3.1 Tuned-CFP Speedup over Simultaneous-CFP                                          |

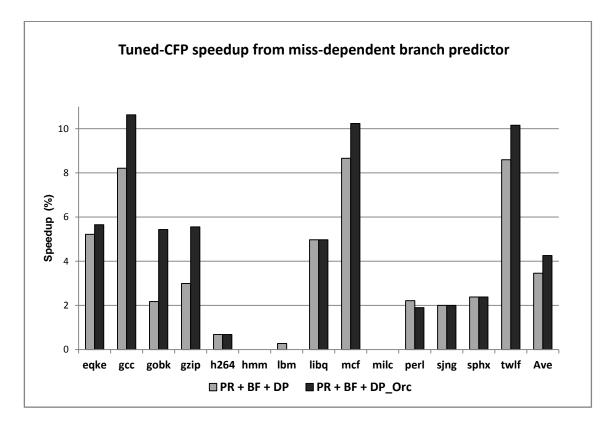

|       | 7.2.3.2 Tuned-CFP Optimizations                                                          |

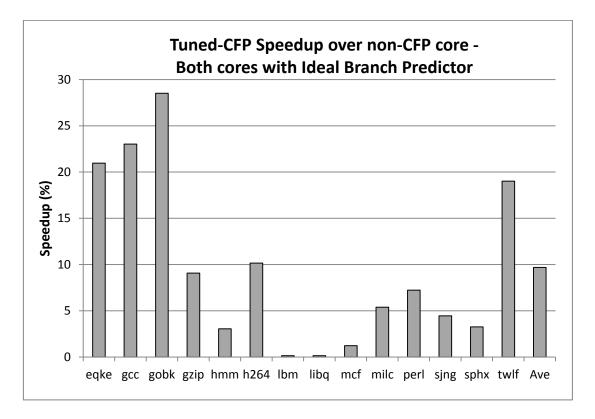

|       | 7.2.4 Performance of Cores with Ideal Branch Predictor                                   |

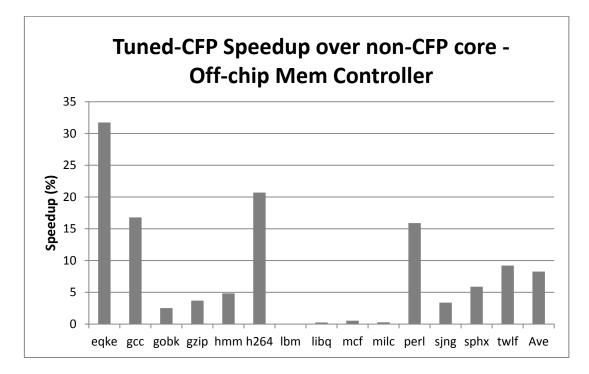

|       | 7.2.5 Performance of Cores with Off-chip Memory Controller1                              |

|       | 7.2.6 Performance of Speculative Cache and SRL                                           |

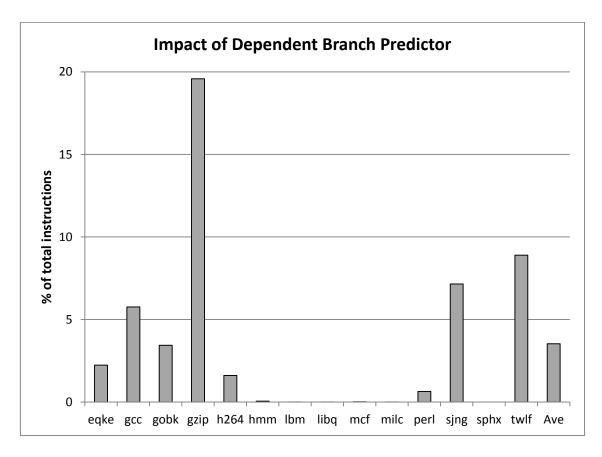

|       | 7.2.7 Performance of Miss-dependent Branch Predictor                                     |

| 7.3 E | valuating Energy per Instruction                                                         |

|       | 7.3.1 Energy per Instruction Comparison of Tuned-CFP and non-CFP Cores                   |

|       | 7.3.2 Energy per Instruction Comparison of S-CFP and Tuned-CFP                           |

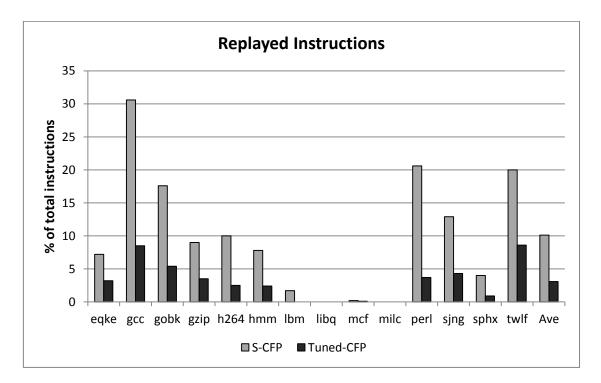

|       | 7.3.2.1 Reduction in Replayed Instructions                                               |

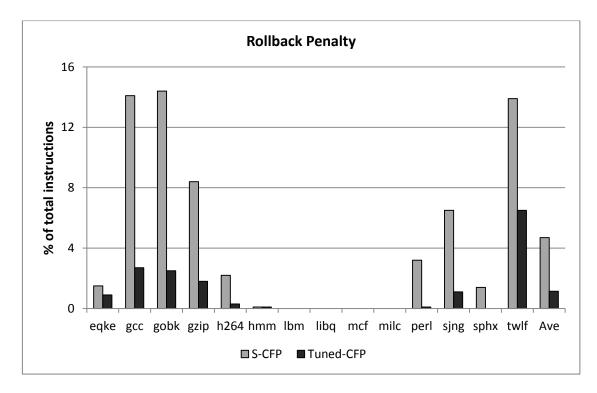

|       | 7.3.2.2 Reduction in Rollback Penalty                                                    |

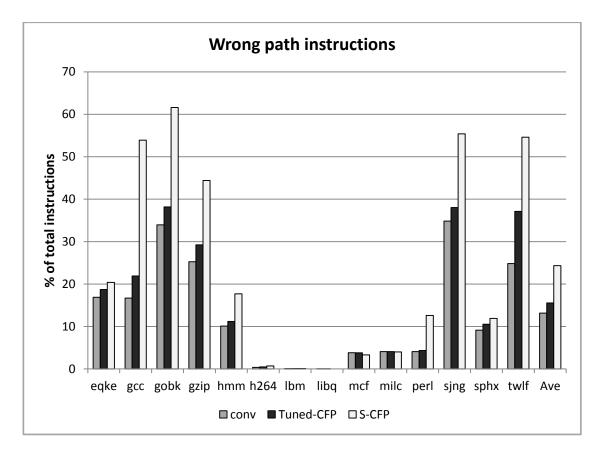

|       | 7.3.2.1 Reduction in Wrong Path Instructions                                             |

| 8. QUALITATIVE ANALYSIS119                                                           |

|--------------------------------------------------------------------------------------|

| 8.1 Qualitative Energy Efficiency Analysis of SRL Mechanism119                       |

| 8.2 Tuned-CFP Performance with Data Prefetch                                         |

| 8.3 Qualitative Comparison of Tuned-CFP with Other Latency Tolerant<br>Architectures |

| 9. CONCLUSIONS 124                                                                   |

| 9.1 Future Work 125                                                                  |

| REFERENCES127                                                                        |

# **ILLUSTRATIONS**

| Figure                                                                                                                                                       |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

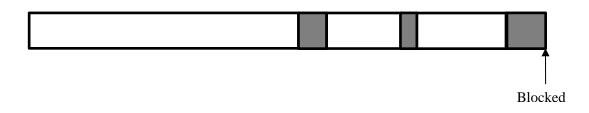

| 1. Execution sequence of an in-order processor when instructions miss the cache                                                                              | 3  |

| 2. Impact of a perfect cache on performance                                                                                                                  | .4 |

| 3. Reorder buffer stalls and reservation stalls in conventional processors                                                                                   | 6  |

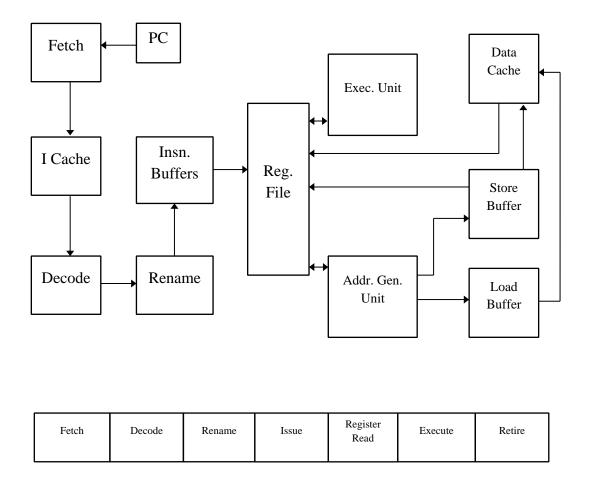

| 4. Execution sequence of an out-of-order execution processor                                                                                                 | 14 |

| 5. Block diagram and pipeline of a conventional superscalar processor                                                                                        | 15 |

| 6. Typical behavior of programs showing ILP behind blocked cache misses                                                                                      | 20 |

| 7. Execution sequence of a Runahead processor                                                                                                                | 22 |

| 8. Execution sequence of a processor that uses WIB                                                                                                           | 24 |

| 9. Execution sequence demonstrating the pipeline flush limitation of conventional-CF                                                                         |    |

| 10. Virtual register renaming architecture block diagram                                                                                                     | 38 |

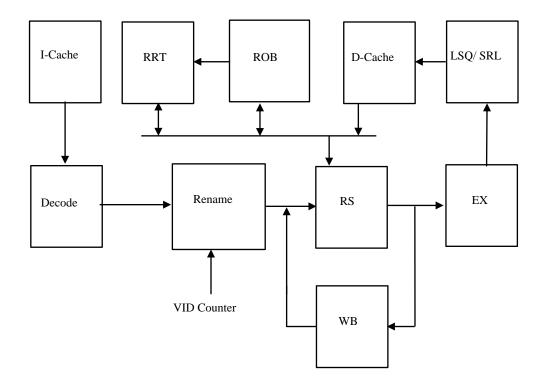

| 11. Simultaneous-CFP architecture block diagram                                                                                                              | 41 |

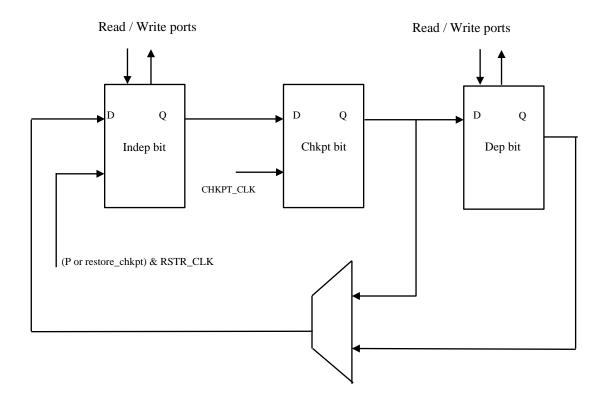

| 12. S-CFP register file cell                                                                                                                                 | 47 |

| 13. Execution sequence showing S-CFP moving a dependent into WB eagerly                                                                                      | 50 |

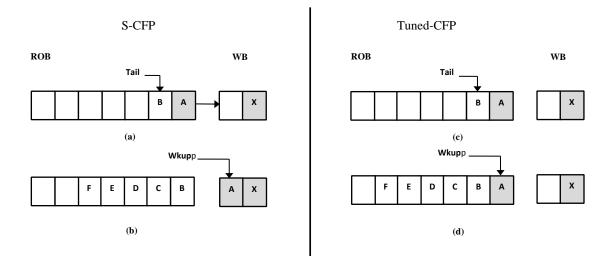

| 14. Execution sequence showing a scenario leading to rollback in S-CFP which is avoided in Tuned-CFP                                                         | 51 |

| 15. Comparison of full replay in S-CFP and partial replay in Tuned-CFP                                                                                       | 52 |

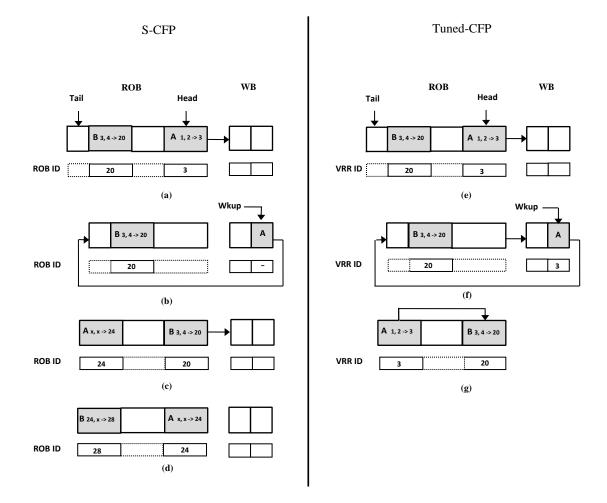

| 16. Limit studies showing potential speedup from buffer full, Oracle miss-dependent branch predictor, minimum replays, individually and combined             |    |

| 17. Block diagram of CFP architecture with virtual register renaming                                                                                         | 60 |

| 18. Working of SRL algorithm with an execution sequence                                                                                                      | 75 |

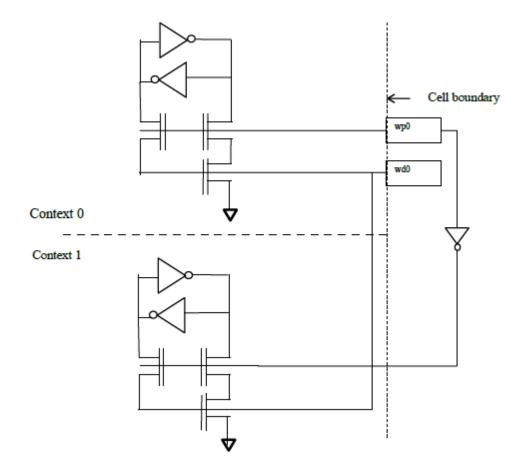

| 19. Single ended read ports                                                                                                                                  | 84 |

| 20. Write mechanism – 4 write ports                                                                                                                          | 84 |

| 21. Percent speedup of non-CFP 4-wide superscalar cores of different instruction buff<br>configurations and ideal data cache over minimal configuration core |    |

| 22. ROE of non-CFP core with ideal data cache for different buffer configurations 89                                              |

|-----------------------------------------------------------------------------------------------------------------------------------|

| 23. ROE of non-CFP core with 8KB L1 D-cache for different buffer<br>configurations                                                |

| 24. Percent speedup of Tuned-CFP over non-CFP core for EFF, DIM and HP<br>models                                                  |

| 25. Speedup of Simultaneous-CFP and Tuned-CFP over Conventional-CFP94                                                             |

| 26. Tuned-CFP percent speedup over simultaneous-CFP                                                                               |

| 27. Percent speedup contribution from miss-dependent branch predictor 98                                                          |

| 28. Speedup of Tuned-CFP over conventional non-CFP superscalar when both cores are simulated with a perfect branch predictor      |

| 29. Speedup of Tuned-CFP over conventional non-CFP superscalar when both cores are simulated with off-chip memory controller      |

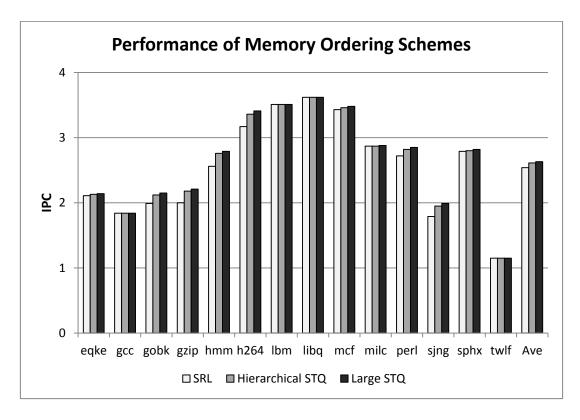

| 30. IPC comparison of SRL, hierarchical STQ and large STQ memory ordering mechanisms                                              |

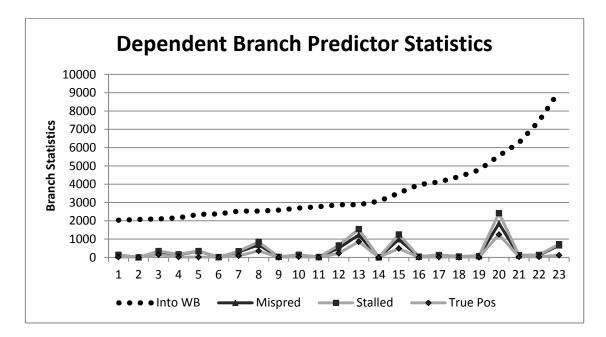

| 31. Correlation between dependent mis-predicted branch and its PC address for<br>branches replayed between 1000 and 10000 times   |

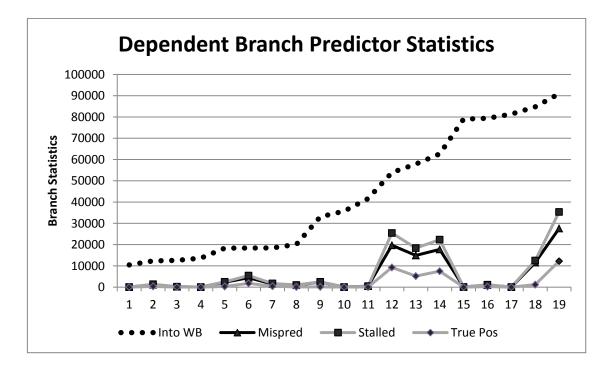

| 32. Correlation between dependent mis-predicted branch and its PC address for<br>branches replayed between 10000 and 100000 times |

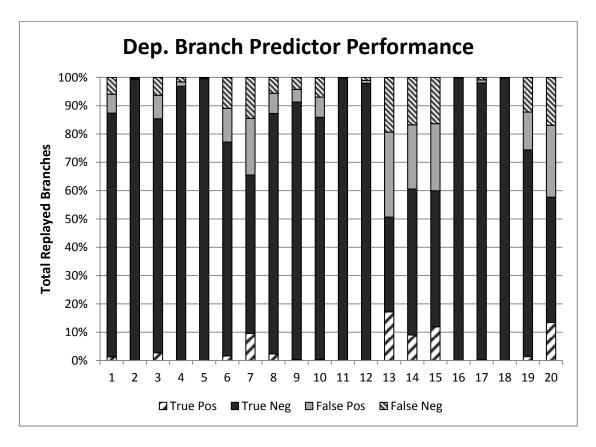

| 33. Dependent branch predictor statistics                                                                                         |

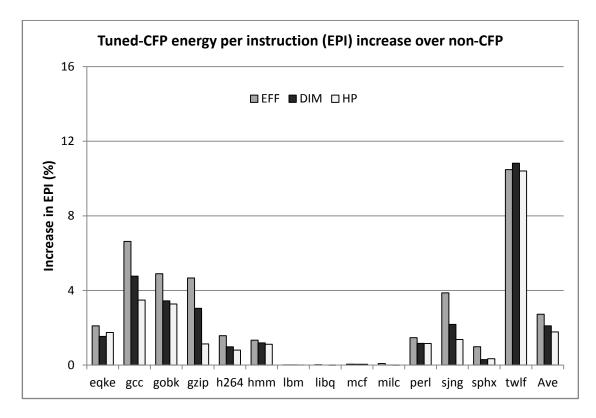

| 34. Tuned-CFP percent increase in EPI compared to non-CFP EFF, DIM and<br>HP models                                               |

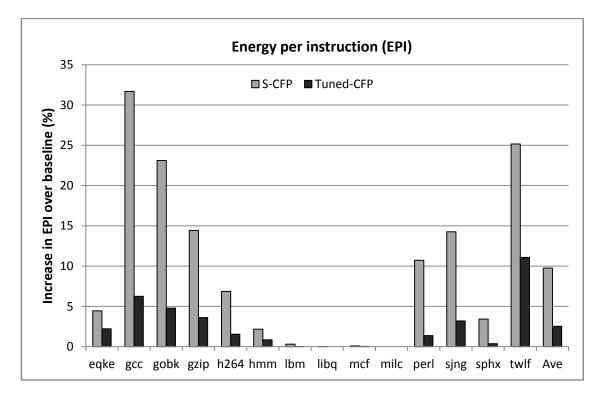

| 35. Energy per instruction % increase of S-CFP and Tuned-CFP over ROB baseline                                                    |

| 36. Percentage of replayed instructions over total instructions in S-CFP and Tuned-CFP.                                           |

| 37. Reduction in rollback penalty in Tuned-CFP compared to S-CFP112                                                               |

| 38. Percentage of wrong path instructions over total instructions in conventional non-<br>CFP, Tuned-CFP and S-CFP cores          |

| 39. Percentage reduction in wrong path instructions in Tuned-CFP core when dependent branch predictor is used                     |

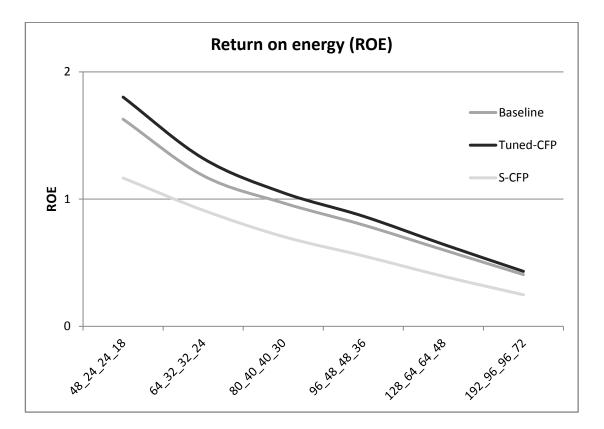

| 40. Return on energy of non-CFP baseline, Tuned-CFP and S-CFP cores 117                                                           |

# TABLES

| Table                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------|

| 1. Summary of speculative accesses to the cache                                                                   |

| 2. Simulated Machine Configuration                                                                                |

| 3. Details of benchmarks                                                                                          |

| 4. Simulation statistics of Tuned-CFP                                                                             |

| 5. Branch instruction statistics of Tuned-CFP100                                                                  |

| 6. Replay, rollback, wrong path and STQ forwarding statistics for SRL mechanism 103                               |

| 7. Speculative load statistics for SRL mechanism                                                                  |

| 8. Speculative store statistics for SRL mechanism                                                                 |

| 9. S-CFP and Tuned-CFP average increase in energy % relative to non-CFP ROB superscalar                           |

| 10. Tuned-CFP percent improvement in ROE over non-CFP. ROE computed relative to 32_16_16_12 non-CFP configuration |

| 11. Area and power comparison of Hierarchical STQ design and SRL design                                           |

# CHAPTER 1 INTRODUCTION

### **1.1 Motivation**

Over the last 20 years, the range of applications that can be run on a computer processor have evolved considerably. Some tasks which were considered impractical in the past, for example, video conferencing between two parties or streaming high quality multimedia, are being done with ease. So with the never ending demands placed by upcoming applications on processors, the onus is on computer architects to design better performing processors. In the past, the goal of a computer architect was fairly straight forward. A processor was designed to run as fast as possible without any compromises. These days with the battery life of mobile devices being critical and large budgets dedicated to cooling servers, energy consumption is an equally important aspect.

The need for energy efficient performance has led to the proliferation of multicore processors, with the first multicore processor released by IBM in 2001. The energy efficiency of multi-core designs comes from building distributed structures as against centralized ones, thus avoiding the quadratic costs associated with scaling the centralized structures for single-thread performance. For instance, four structures of size N consume less energy than one structure of size 4N [38]. Similarly, four structures with one port each consume less energy than one structure with four ports, and four cores operating at 1GHz consume less energy than one core operating at 4GHz [1]. Multi-core processors are efficient either for throughput performance or when there are explicitly written parallel programs available to take advantage of multiple execution

1

resources. In addition to parallel applications there are many important single-threaded applications already in use which are difficult to parallelize. Future multi-core processors should be able to run both parallel and single-threaded applications efficiently. No matter how many parallel cores are integrated on a chip, it is the performance of single thread programs, i.e. the slowest portion of code, which will dominate overall performance according to Amdahl's Law [16]. Hence it is critical to obtain single-thread performance using energy efficient methods.

So in view of these points, computer architects are presented with a new challenge: how to provide energy efficient single-thread performance for applications that are hard to parallelize, while placing on a single die as many cores as possible for high throughput performance.

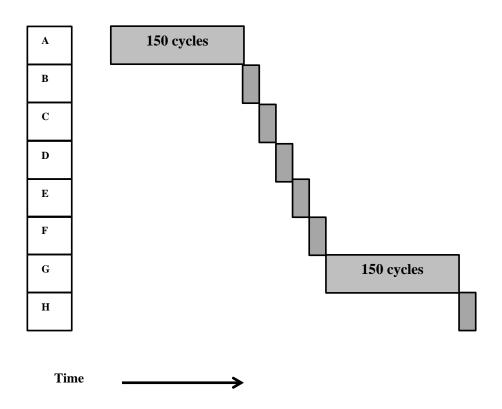

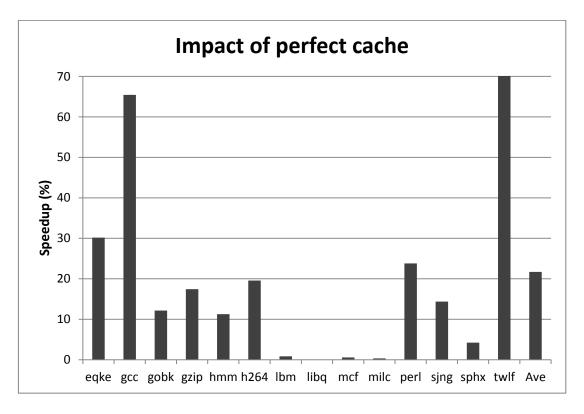

One of the main factors that impact processor performance is data cache misses. Figure 1 shows the example of an execution sequence of eight instructions A to H in an in-order processor. Instructions A and H miss the cache and hence take a long time (shown as 150 cycles) to complete. Even though the rest of the instructions are independent of the cache miss and can complete soon, the overall execution time is dominated by the time needed to service the cache misses. Figure 2 shows the speedup of a processor core with perfect cache over a core with practical cache configuration. Many memory bound programs like gcc and twolf benefit immensely from not having to stall because of cache misses. How can these stalls be avoided?

Since the introduction of Intel P6 architecture in 1996 [39], the capacity of instruction buffers, such as reorder buffers, reservation stations and load and store queues [44], and the size of on-chip caches have kept increasing with every new generation of out-of-order core. The motivation behind this continuous evolution

2

Figure 1. Execution sequence of an in-order processor when instructions miss the cache

towards larger buffers and caches has been performance of single-thread applications. Achieving performance this way has come at the expense of area, power, and complexity. At the circuit level, larger L1 data caches and multi-ported, timing critical instruction buffers, such as the store queue, the reorder buffer, the register file and the reservation stations, have become increasingly difficult to design while maintaining high clock rates. Designers have had to increase the degree of pipelining to meet cycle time, for example adding pipe stages to the first level data cache and the store queue.

The critical circuit paths introduced by larger instruction buffers and the increased pipelining have led to high complexity in the logic design as well. In fact, core complexity has risen so much that adding almost any new performance feature

Figure 2. Impact of a perfect cache on performance

requires significant design validation effort. By increasing instruction buffer sizes designers have been seeking performance benefits from three different sources:

1. With larger buffers, the scheduling hardware has a larger pool of instructions from which to dynamically identify and schedule independent instructions concurrently, thus taking advantage of the wide pipeline and multiple functional units.

2. Increased instruction level parallelism from larger instruction windows reduces the impact on performance of stalls from multi-cycle instructions, e.g. floating point, load, multiply, or divide instructions.

3. Finally, larger buffers allow hardware to find instructions to execute behind very long latency instructions, such as loads that miss the data cache, thus reducing the impact of cache miss data hazards on performance.

For two decades, increasing instruction buffers has provided good performance improvement due to the benefits listed above. However, we have reached an end point [1]. Current buffer sizes are more than sufficient for code that hits the L1 data cache (benefits 1 and 2 above), and way too small for code that misses the L1 data cache (benefit 3 above). Load latency to the last level cache on current multicore processors is more than 20 clock cycles, and latency of load miss to DRAM, even in the best case of on-chip DRAM controller, is significantly more than hundred cycles. It is simply not practical to increase instruction buffer sizes to the capacity necessary to handle long load latencies to the last level cache or to DRAM.

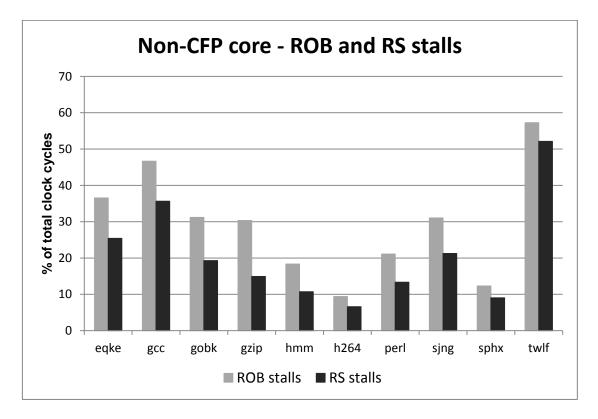

Figure 3 shows the percentage of reorder buffer stalls and reservation station stalls over total execution time in a typical superscalar processor. From the figure it is clear that even with reasonably sized buffers, conventional processors fill up soon and quickly run out of instructions to retire in case of the reorder buffer, or execute in case of reservation stations and spend a considerable fraction of execution time sitting idle.

A different design strategy would be to size the instruction buffers to the minimum size necessary to handle the common case of L1 data cache hit and use less circuit critical and power hungry mechanisms to handle code that misses the L1 data cache, assuming such mechanisms exist. In fact, there have been various studies of latency-tolerant architectures that target reducing the impact of data cache misses on performance, without having to increase instruction buffer sizes

[7][9][10][17][32][37][46]. These architectures have common characteristics, but vary in implementation details. They all tolerate cache miss latencies by managing buffer resources in a non-conventional way. Instructions that depend on a cache miss do not block the execution pipeline. Instead, they move with any ready source registers into a

5

Figure 3. Reorder buffer stalls and reservation station stalls in conventional processors

buffer outside the execution pipeline, implemented as SRAM FIFO buffer to minimize area and power, thus allowing look-ahead execution and pseudo-retirement of independent instructions to continue without stalling the pipeline. When the miss data is loaded into the cache, the miss dependent instructions are dispatched back from the FIFO buffer into the execution pipeline. When the execution of the miss dependent instructions completes, results of the independent and dependent instructions are merged together and then execution resumes normally until another load instruction misses the data cache. Since independent instructions complete and pseudo-retire before older instructions that depend on the data cache miss, all these architectures use checkpoints [2][3] to recover from branch mis-predictions and exceptions that depend on the miss. All previous latency-tolerant architectures either target last level cache misses to DRAM [9][10][32][46] or use small in-order cores for high-throughput many-core processors [7][17][37]. Unfortunately, in-order architectures provide limited singlethread performance as compared to out-of-order cores, and latency-tolerant performance techniques that target cache misses to DRAM provide less benefit nowadays than on previous generations of processors. This is because large on-chip caches and integrated on-chip memory controllers, typical on current main stream processors, reduce (but not completely eliminate) the overall impact of accesses to DRAM. Still unexploited in latency-tolerant out-of-order core proposals are misses to the L1 data cache that hit L2 and L3 on-chip cache. These misses cause shorter delays than misses to DRAM, but they occur a lot more frequently and consequently have as much impact on performance as misses to DRAM on many applications. Therefore, new out-of-order cores that can handle not only cache misses to DRAM, but cache misses at all levels of the cache hierarchy, without having to increase buffer sizes, are needed to increase energy efficiency and performance of single-thread applications.

Continual Flow Pipeline architecture [46] is one such proposal that attempts to tolerate long latencies of only last level cache misses that go to DRAM. In that work, the miss-independent and miss-dependent instructions execute at different times, based on the timing of the load miss event and the data arrival event. Switching between the two executions is costly because it involves a pipeline flush, making this proposal unsuitable for L1 misses that hit the on-chip cache. To avoid this costly pipeline flush, we propose to execute the independent and dependent instructions simultaneously, thus making this proposal, which we call Simultaneous-CFP, more suitable for first level data cache misses. However, in Simultaneous-CFP, many applications or execution

phases of applications incur excessive amount of replay and rollbacks to checkpoints because of miss-dependent branches that mis-predict. Excessive replay increases the chance of replaying mis-predicted branches and consequently rollbacks to the checkpoints. This frequently cancels any desired improvement resulting from S-CFP handling of L1 data cache misses and can even cause performance degradation. In order to overcome these limitations, we use a novel virtual register renaming substrate [24][41] and fine tune the replay policies to mitigate excessive replays and rollbacks to the checkpoint. We call this Tuned-CFP processor core architecture.

### **1.2. Dissertation Contribution**

In this dissertation, we propose a processor core architecture that overcomes the limitations of previous latency tolerant processor architectures and make the following contributions –

1. We introduce novel out-of-order execution algorithms that extend Continual Flow Pipelines [46] to allow L1 data cache miss independent instructions and dependent instructions, widely separated within a single-thread program, to execute simultaneously in the core pipeline. This allows our architecture to handle effectively first level cache misses that hit the higher level on-chip cache, as well as cache misses to DRAM. We call this architecture Simultaneous Continual Flow Pipeline (S-CFP).

2. To support the Simultaneous-CFP core architecture, we present novel algorithms for performing fast register results integration and load-store memory ordering while executing simultaneously in the core pipeline non-contiguous miss dependent and independent instructions.

3. We see that Simultaneous-CFP incurs a lot of circuit activity due to excessive replay of load miss dependent instructions. In an attempt to fine tune the replay policies, we keep the miss-dependent instructions in the reservation stations as long as possible after the miss before they are evicted to the waiting buffer. This reduces the number of miss-dependent instructions that are replayed in case of medium latency load misses, which are those loads that miss the L1 data cache but hit the L2 data cache.

4. We remove the reorder buffer from the replay loop in order to reduce the replay latency of miss-dependent instructions that are evicted to the waiting buffer and thus reduce the total execution time. For this, we use an order list of instructions in the reservation stations to order miss-dependent instructions when they have to move into the waiting buffer.

5. On CFP architectures, all miss-dependent instructions have to be moved into the waiting buffer and then replayed, once the load miss is moved into the waiting buffer. This is necessary since when the miss load pseudo commits and moves into the waiting buffer, it releases its renamed destination register ID (also called tag). This breaks the dependence links between the miss load and its dependents, requiring the full dependence chain to be replayed and renamed again to re-establish the dependence links. In this dissertation, we use virtual register renaming [41], which allows partial replay of the miss load and its dependents, thus significantly reducing the number of replayed instructions and the total execution time.

6. On CFP architectures, mis-predicted branches that depend on load misses have very high mis-prediction penalty. The reason is that CFP recovers from these mispredictions by rolling back execution to a checklepoint taken at the load miss. Reducing the number of replayed instructions reduces the chance of encountering miss-dependent branch mis-predictions and their high recovery penalty. This improves performance significantly on benchmarks that have many branches that depend on load misses.

7. Branch instructions that move into the waiting buffer and later found to be mis-predicted not only degrade performance but also increase power consumption significantly because of the large number of wrong path instructions burning processor resources wastefully. This dissertation presents a hardware predictor that is used as a branch confidence mechanism to identify miss-dependent branches that are likely to mis-predict, and stalls the pipeline when such low confidence branches are moved into the waiting buffer. This prediction mechanism reduces execution waste and as a result power consumption on benchmarks that have many mis-predicted branches that depend on load misses.

8. Finally, using a microarchitecture performance simulator and architectural level power model, it shows that the optimized CFP architecture, which we call Tuned-CFP, improves execution time and energy consumption by 10% and 8% respectively over S-CFP architecture. This dissertation also shows that as the instruction buffer sizes are scaled over a wide range, the Tuned-CFP architecture consistently provides better performance return on energy per instruction compared to conventional reorder buffer superscalar architecture and previous latency tolerant architectures.

### **1.3 Dissertation Related Publications**

1. Simultaneous continual flow pipeline architecture. In *Proceedings of 29<sup>th</sup> IEEE International Conference on Computer Design*. IEEE, 127-134. Oct 2011. 2. Virtual Register Renaming: Energy Efficient Substrate for Continual Flow Pipelines. In *Proceedings of the 23rd Great Lakes Symposium on VLSI*. ACM, 43-48. May 2013.

3. Tuning the Continual Pipeline Architecture. In *Proceedings of the* 27<sup>th</sup> *International Conference on Supercomputing*. ACM, 243-252. June 2013.

4. Streamlining the Continual Flow Processor Architecture with Fast Replay Loop. In *Proceedings of the IEEE International Conference on Computer as a Tool.* EUROCON. IEEE, 1821-1828. July 2013.

5. Tuning the Continual Pipeline Architecture with Virtual Register Renaming. In *ACM Transactions on Architecture and Code Optimization*. ACM, Accepted November 2013.

### **1.4 Document Organization**

The rest of the document is organized as follows. Chapter 2 talks about related work on latency tolerance for cache misses. Chapter 3 talks about Simultaneous-CFP architecture and its limitations, and presents a limit study to measure the upper bound on performance when all its limitations are addressed. Chapter 4 talks about Tuned-CFP architecture which is built on a virtual register renaming substrate and also fine tunes many replay policies of Simultaneous-CFP. Chapter 5 details the memory organization of an architecture that supports simultaneous execution of miss-dependent and miss-independent instructions. Chapter 6 talks about the experimental setup. Chapter 7 presents experimental results. Chapter 8 makes qualitative comparisons between Tuned-CFP and earlier latency tolerant proposals. Chapter 9 concludes and talks about the scope for future work.

# CHAPTER 2 BACKGROUND WORK

The objective of this dissertation is to provide energy efficient load latency tolerance for better performance. In this chapter we will talk about the techniques that have been proposed in literature and used in practice to provide load latency tolerance in processors. The first section will talk about the conventional techniques used in commercial processors and explain why future processors cannot employ the same techniques to gain performance. The second section will talk about unconventional techniques proposed in literature to support large instruction windows without scaling cycle critical buffers. The third and fourth sections will talk about two concepts that aid the application of CFP to first level misses and keep the processor energy efficient – one is simultaneous multithreading that allows miss-dependents and miss-independents to execute concurrently; the other is virtual register renaming, an essential substrate on which our latency tolerant architecture is built.

### 2.1 Conventional Mechanisms Used in Commercial Processors

As mentioned before, commercial processors have been building wider machines and larger instruction buffers and on-chip caches to provide performance by exposing instruction level parallelism (ILP) and memory level parallelism (MLP) [44]. ILP occurs when the processor finds some independent instructions to execute while the load miss data is being fetched from the higher level memory. MLP occurs when the processor overlaps the memory access latency of independent load misses. Both forms of parallelism are limited to how far the processor can look ahead in the program to seek instructions that can be scheduled for execution. The way this works is explained with an example below.

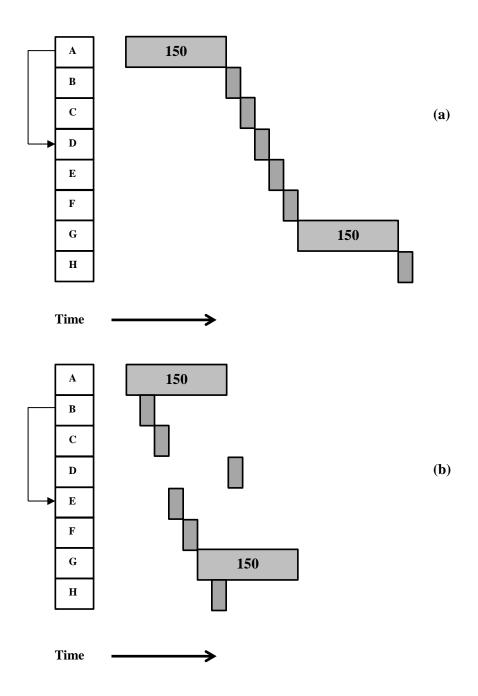

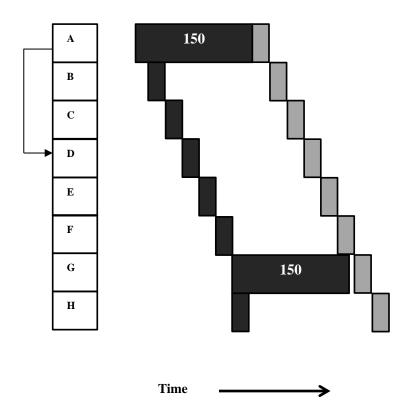

Figure 4(b) shows the working of a conventional out-of-order processor. To understanding its working, the execution sequence of an in-order processor is also shown above it in Figure 4(a). In Figure 4 there are eight instructions A-H. A and G miss the last level cache and hence take a long time to execute, with their latency shown as 150 cycles. The other instructions are of short latency and can finish quickly. Instruction D depends on A as shown by the arrow from A to D. In an in-order processor, there is no re-ordering of instructions based on them becoming ready, so the misses serialize and in the end the 8 instructions take a long time to finish.

An out-of-order processor can achieve some performance gains as shown in Figure 4(b). When A misses the cache and while its data is being fetched, independent instructions B, C, E, F and H are scheduled for execution. The MLP comes from the fact that both misses A and G can be overlapped together, so that G does not spend additional time waiting for its data. At the same time, some ILP comes from the fact that B, C, E, F and H can be executed while A and G wait for their data to arrive. From this example, it can be seen that a large out-of-order window benefits performance. However the structures that support out-of-order execution are not energy efficient.

The organization of a conventional reorder buffer based superscalar processor will be explained next.

### 2.1.1 Microarchitecture of a Conventional Superscalar

Figure 4. Execution sequence of an out-of-order execution processor

A conventional superscalar architecture and its pipeline are shown in Figure 5. This superscalar processor fetches a block of instructions every cycle. The fetch unit controls fetching using branch prediction, a branch target buffer (BTB), and a procedure

Figure 5. Block diagram and pipeline of a conventional superscalar processor

return address stack (RAS). Fetched instructions are decoded and passed to the rename unit, which maps logical registers into a set of physical registers, removing false dependencies. Instructions are then placed in the issue queue where they remain until they get a chance to execute, i.e. their source operands become available. The instructions execute out-of-order based on when their sources become ready and release their issue queue entries upon completion. The instructions are retired in program order after completing execution, freeing physical registers that are no longer needed. Loads and stores are issued to address generation units. Stores are then written into a store buffer, speculatively, where they remain until retirement. At retirement, stores update the data cache, but this time non-speculatively in program order. A load is sent with its address to the load buffer, store buffer, and the data cache unit. Its data is written back from the store buffer or cache to the register file, speculatively, if there is no address resolution conflict in the store buffer. If there is an address conflict or the memory dependence predictor detects a dependency, the load waits in the load buffer until the conflicting address in the store buffer is resolved. If a load is found to have been prematurely scheduled, the load does not have to re-fetched, since it a correct instruction that has executed with incorrect data. It is simply reissued for execution or *replayed* with correct data. If a branch is found to be mis-predicted, the pipeline is flushed and all speculative state following the branch is discarded.

The main cycle critical structures in a superscalar processor are physical registers, issue queue and load store queues.

### 2.1.2 Problems with Scaling Physical Register File

In some implementations [39], the reorder buffer [43] is used for the purpose of register renaming, so we will discuss the energy efficiency issues of a reorder buffer with respect to the physical register file array [43]. Register renaming is a technique employed by out-of-order processors where a larger set of physical registers in addition to the architectural registers are used to overcome false dependencies between instructions that come as an artifact of limited logical registers in the instruction set architecture (ISA) [43].

Assuming each instruction has two source registers and one destination register, the register file needs two read ports and one write port for every instruction. So, on a 4 wide machine, it needs approximately 8 read ports and 4 write ports. In some implementations this can be reduced to a lower number because some instructions get their data from the bypass network and instructions like branches and stores do not need the write port as they do not produce results that need to be written to the register file. In any case, the complex implementation and power inefficiency of the large number of ports needed to support a wide machine and large instruction window makes the register file a difficult structure to scale.

### 2.1.3 Problems with Scaling Issue Queue

The reservation station (RS) or issue queue holds all the instructions that have been renamed but are yet to execute [45]. The working of a reservation station involves two actions – 1) finding instructions that can be scheduled for execution. 2) After an instruction finishes execution, waking up other instructions which are waiting for the result produced by the completing instruction. Scheduling ready instructions is typically implemented as a priority encoder. The wakeup logic is implemented as content addressable memory (CAM) matching logic where every entry in the reservation station matches its source ID with the ID of a completing instruction to find out if its source is ready. This CAM logic is associative and as a result, the RS implementation involves a lot of dynamic activity and power consumption. At the same time, The RS logic is on the critical path and cannot take multiple cycles because dependent instructions need to be woken up and scheduled for execution in consecutive clock cycles to ensure good performance. For this reason the wakeup logic is usually designed to have minimum possible latency. These two reasons make the implementation of large reservation stations very difficult.

17

### 2.1.4 Problems with Scaling Load Store Queue

In addition to instructions that access registers, the instruction window is also made of instructions that access memory. In order to support a large window, conventional processors use a load and store queue [43]. With out-of-order execution and stores completing out-of-order, it is necessary to make sure that a load reads its data from the correct store. Stores write to the cache only in program order for correctness reasons. It hurts performance if a load has to wait for every store to update the cache and then read its data. Just like register data can be forwarded to its sourcing instruction through the bypass network much before the data reaches the register file, there is provision for a store to forward data to its dependent load before it reaches the cache. In order to achieve this store-to-load forwarding, conventional processors use a store queue that holds the address and data of all stores in the instruction window. When a load executes, it searches the entire store queue for an older store to the same address. If there is a hit, it uses the data from the store queue; otherwise, it uses the data from the cache. Typically the store queue and the cache are searched for a matching address in parallel to save on time. The store queue is implemented using CAM logic to match the store address with that of the load. The latency of this associative match should not be worse than that of a cache hit; otherwise the load scheduling logic will become more complex. All these reasons make it difficult to build a large store queue to support a large instruction window for performance.

In conventional processors, the store-to-load forwarding is done speculatively. With out-of-order execution, a load address may become ready before older stores complete. It is very conservative to let a load wait until all stores before it complete, which does not help performance. Typically, processors use a memory dependence predictor to decide whether to stall such a load or schedule it [8]. In some cases a load may read the data from an incorrect store, leading to a memory ordering violation [8]. In order to avoid such memory ordering violations there is a load buffer that holds all the loads in the window in program order. Each retiring store checks with this load buffer if any load has executed prematurely with incorrect data. If a memory ordering violation is detected, corrective action has to be taken, for instance the load will have to be replayed with correct data [19]. This matching of the store address with the load buffer entries is also an associative search, making it non-scalable like the previously discussed structures.

Sections 2.1.2 to 2.1.4 explain the reasons why scaling the instruction buffers to large sizes in order to support a large number of in-flight instructions is neither practical nor energy efficient.

#### 2.2 Mechanisms in Literature

So far it has been established that a large instruction window is needed for good single thread performance, but large instruction buffers cannot be used to achieve this because of their energy inefficiency. Is there an alternative to simply scaling the sizes of instruction buffers for performance?

Earlier work [29][46] on ILP have shown that in an instruction window comprising of both blocked and miss-independent instructions, the blocked instructions are far fewer than independent instructions. As shown in Figure 6, beyond a few dependent instructions, there are a lot of independent instructions which can be scheduled for execution without having to wait for the load miss. The amount of ILP

Figure 6. Typical behavior of programs showing ILP behind blocked cache misses

that can be exposed by a typical out-of-order superscalar processor in the event of a last level load miss is not even comparable to the amount of ILP that exists in programs. For instance, if the window in Figure 6 is of thousands of instructions, a state of the art commercial processor which can support an instruction window of ~200 instructions will soon run out of instruction buffers and stall much before it can reach the majority of independent instructions, thus exposing only limited ILP while dissipating a lot of power in the process. There have been several unconventional processor architectures proposed in literature which take advantage of such program behavior shown in Figure 6 and deal with load misses to the cache in a different way. They unblock the load miss and its dependent instructions and make them release their pipeline resources until the miss data arrives. Since long latency instructions do not hold on to their instruction buffers for a long time, pipeline resources are always recycled quickly, so only a reasonable number of instruction buffers are sufficient to support a large instruction window. These architectures differ from each other in terms of how this large look ahead instruction window is made available, which is explained in the next section.

### 2.2.1 Runahead execution processors

A Runahead execution processor [12][34] exposes MLP in programs in the

event of last level cache misses. When a load misses the cache, a Runahead processor checkpoints [21] the architectural state and enters Runahead mode. The load miss and its dependents pseudo-execute and release their pipeline resources. The miss-independents also complete execution and retire from the reorder buffer. However, in Runahead mode, the retiring instructions do not update the architectural state or cache. When the miss returns the processor state is restored from the checkpoint. All the instructions, both dependents and independents are re-executed with correct data. The only difference is that the execution now is accelerated because the data required by the instructions in the current window is brought to the processor core sooner, owing to the MLP exposed by Runahead execution. All the speculative work done in the shadow of the cache miss is thrown away.

Figure 7 shows the working of a Runahead processor for the same working example from Figure 4. The darker shaded blocks indicate pseudo-execution of instructions while the lighter shaded blocks indicate second wave execution after the miss data is returned to the processor. Figure 7 shows that second wave execution is much faster and involves fewer stalls compared to first wave execution. The same figure also shows that all the instructions are re-executed during the second wave. As for the memory state needed to maintain a large window, since Runahead processors do not update the cache, memory ordering violations in Runahead mode are not fatal. Hence a small load store queue will suffice.

The advantage of Runahead execution is that it is perfectly implementable with negligible hardware overhead needed for the checkpoint. However, notice that Runahead chooses to re-execute all the miss-independent instructions redundantly. In other words, the key problem with Runahead processor is that it does not have provision

Figure 7. Execution sequence of a Runahead processor

to save the results of independent execution and thereby ends up re-executing all the non-shaded instructions in Figure 7 after the miss comes back, even though those instructions are not related to the miss. Since all the speculative work is thrown away there is limited performance improvement from Runahead execution. Moreover, there is wastage of energy because all instructions are executed twice, once in Runahead mode and again when the miss data is delivered. If Runahead cannot expose any MLP then there is no performance benefit, while the energy consumption cannot be avoided. In order to overcome this, later work [35][36], adds heuristics to determine phases where Runahead execution would not benefit. This is done by maintaining a history of load misses that have exposed MLP. If a load that is known to have not given any prefetch benefit misses again, the processor opts not to go into Runahead mode. Another heuristic makes note of the number of instructions pseudo-retired in the runahead window and makes sure atleast these many instructions retire before Runahead mode is entered once again. This heuristic avoids overlapping Runahead episodes. Overall these heuristics improve performance and energy by some amount.

In summary, the Runahead concept is applied to last level misses that typically take a long time to return. Potentially a lot of ILP can be exposed in Runahead mode while the miss is outstanding. The fact that all this work, including meaningful independent execution is thrown away after the miss returns, would be the biggest limiting factor of this proposal.

### 2.2.2 Waiting Instruction Buffer

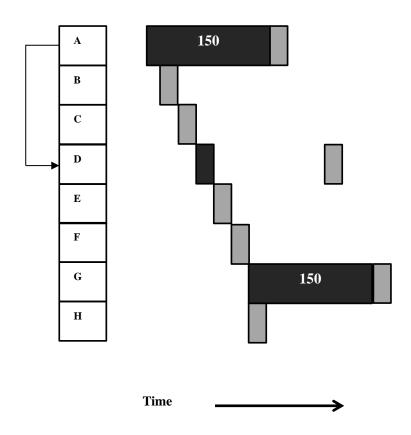

The Waiting Instruction Buffer [30] does what Runahead execution processor does not - which is execute the miss-independent instructions while the load miss is outstanding and not revisit them again after the miss comes back. This is because, unlike Runahead processor, Waiting Instruction Buffer (WIB) provides the ability to retain the results of independent execution, but at the expense of inordinate amount of buffering, as will be explained further.

Typically in a superscalar processor the issue queue size is lower than the size of the instruction window because the reservation stations do not buffer those instructions that have completed but are yet to retire. As mentioned before, the issue queue is a complex structure made up of CAM logic which is also timing critical. The WIB design releases pressure on the issue queue by making long latency cache misses release their issue queue entries. The execution of WIB for the same working example

Figure 8. Execution sequence of a processor that uses WIB

is shown in Figure 8. As can be seen in the figure, the miss-independents B, C, E, F and H do not re-execute when the miss returns; only the load miss and miss-dependent instructions A, D and G do, shown by the presence of both dark and light shaded boxes alongside these instructions. WIB treats the issue queue as the only critical resource and allows miss dependents to retain other pipeline resources like physical registers and load store queue entries, simply assuming that a large number of them can be made available in future implementations. So in order to support a large instruction window, WIB physically buffers the entire window with a multi-level register file and large instruction buffers. In WIB, each instruction dependent on a load miss sets a bit vector dedicated for each outstanding miss, which allows miss-dependents to be reissued post

wakeup without needing the complex broadcast logic of the issue queue. Their waiting buffer is organized as a multi-banked structure which allows miss-dependents to be reissued in any order as and when the wakeup arrives. Physically buffering the entire instruction window also allows instructions dependent on multiple load misses or missdependent misses to be moved in and out of the issue queue multiple times, although at the cost of excessive re-execution and energy.

In summary, WIB is able to exploit large amount of ILP by executing the missindependents while the load miss is outstanding and does not re-execute these instructions when the miss data returns. However, it achieves this by physically buffering the entire instruction window, the implementation of which is impractical.

### 2.2.3 Continual Flow Pipelines

Continual Flow Pipelines [46] was the first latency tolerant proposal that included scalable solutions for the all the cycle critical pipeline resources including the register file, issue queue and load/store queues. This dissertation aims to improve on the latency tolerance techniques proposed in conventional CFP.

When a load miss occurs, CFP makes the load miss and its dependents relinquish their critical pipeline resources and wait in a low complexity FIFO buffer outside the core pipeline. Repeating the running example, CFP execution would look exactly the same as the execution of WIB shown in Figure 8. The primary difference is that CFP incorporates a scalable register management algorithm and addresses issues with scaling the load and store queue issues in addition to the issue queue.

# 2.2.3.1 Register Management in CFP

CFP alleviates pressure on the register file by replacing conventional ROBbased register management with Checkpoint Processing and Recovery (CPR) [2][3]. CPR operates at the granularity of checkpoints, which are created at the rename stage. Instructions are bulk committed one checkpoint at a time and recovery is permitted only to checkpoints. CPR takes advantage of this recovery restriction to aggressively reclaim physical registers between checkpoints. CPR tracks registers by associating each register with a reference count and a count of zero indicates the register is free. A register's reference count is incremented when an instruction that reads or writes the register is dispatched to the issue queue and decremented when that instruction executes or is squashed.

#### 2.2.3.2 Slice Buffer Management in CFP

CFP releases pressure on the issue queue by making miss-dependent instructions release their issue queue entries, similar to WIB, and moving them outside the critical pipeline into a low complexity slice buffer. While CFP's slice buffer is similar to WIB, it has two important differences. First, while WIB physically buffers the entire instruction window, CFP buffers only the miss-dependents, which are far fewer in number compared to the miss-independents [28][46], as shown in Figure 6. This allows CFP to support a large instruction window with a reasonably small slice buffer. Second, in CFP miss-dependent instructions capture miss-independent register inputs when they move into the slice buffer. This decouples the miss-dependent slice from the rest of the program. This decoupling means that miss-dependent instructions can release their input registers as if they had executed, allowing CPR to reclaim them long before they are used by the slice buffer instructions.

The CFP slice buffer is maintained in execution order and instructions are allocated slice buffer entries as they come out of the issue queue. After the wakeup, CFP re-introduces the instructions from the slice buffer into the pipeline by re-renaming and re-dispatching them. Since CFP populates the slice buffer in execution order, the slice buffer cannot represent register dependences in terms of logical register names (since logical registers may have been overwritten by the miss-independent instructions)) and hence must use physical register names instead. So CFP uses a physical-to-physical register renaming policy to reintroduce slice instructions into the pipeline. In physicalto-physical registers. An instructions input registers are renamed by indexing this map table with the physical register numbers that it received when it was originally renamed. A new destination register is allocated, and entered into the map table at the index corresponding to the destination physical register number originally assigned at rename.

#### 2.2.3.3 Load and Store Management in CFP

CFP scales the load and store queues through the use of hierarchy [2]. To support a large window of load instructions, CFP uses a conventional fully-associative first level load queue along with a large set-associative second level load queue [2]. In this hierarchical design, the youngest loads are placed in the fully-associative queue. When the fully-associative queue fills up, the oldest load in the queue is relegated to the set-associative load queue. CFP also uses hierarchy to manage stores [2]. Similar to the load queue design there is a conventional first level store queue and a larger associative second level store queue with slower access latency. This is known to work well because store-load pairs are usually within a short distance from each other and most of the forwarding occurs when a store is still in the first level store queue. This is the main purpose of the first level store queue while the second level store queue is used mainly to ensure memory ordering. Though hierarchical store queues perform well, the disadvantage with a large second level store queue is the area and energy inefficiency of the CAM matching circuitry [14].

To overcome the dynamic power associated with a large associative hierarchical store queue, Gandhi et. al. propose to replace it with a simple FIFO structure called the Store-Redo Log (SRL) [14] that records all the stores in the instruction window in program order. All completing stores write their data into preallocated locations (assigned at rename) in the SRL whenever they become ready.

While the miss is pending, miss-independent stores write to the cache speculatively and also update the SRL. Miss-independent loads which cannot forward data from the small conventional store queue get their data speculatively from the cache. When the miss returns, the speculative state in the cache is flushed and the slice buffer instructions are reissued for second wave execution. Miss-dependent stores get store queue entries to forward data to dependent loads. When miss-dependent stores complete, they fill up the holes in the SRL buffer assigned for dependent stores. When the slice buffer empties, all the holes in the SRL are filled up by either independent or dependent stores. Then all the stores are emptied into the cache in program order from SRL.

28

Notice that the miss-independents write to the cache twice, first time for forwarding data to independent loads and second time from the SRL in correct program order. The advantage of the SRL is that it does not take part in any forwarding and is neither a multi-ported nor an associative structure. It is primarily there to ensure store updates to the cache take place in program order, while the responsibility of forwarding is off-loaded to the small store queue and cache. This allows the SRL design to support a large window and yet remain scalable.

### 2.2.3.4 CFP on In-order Processors

CFP on in-order cores was first proposed in [37]. This approach is suitable for highly energy constrained computing devices but less suitable for the performance needs of conventional single-thread applications targeted by the Tuned-CFP multicore architecture.

# 2.2.3.5 Limitations of CFP

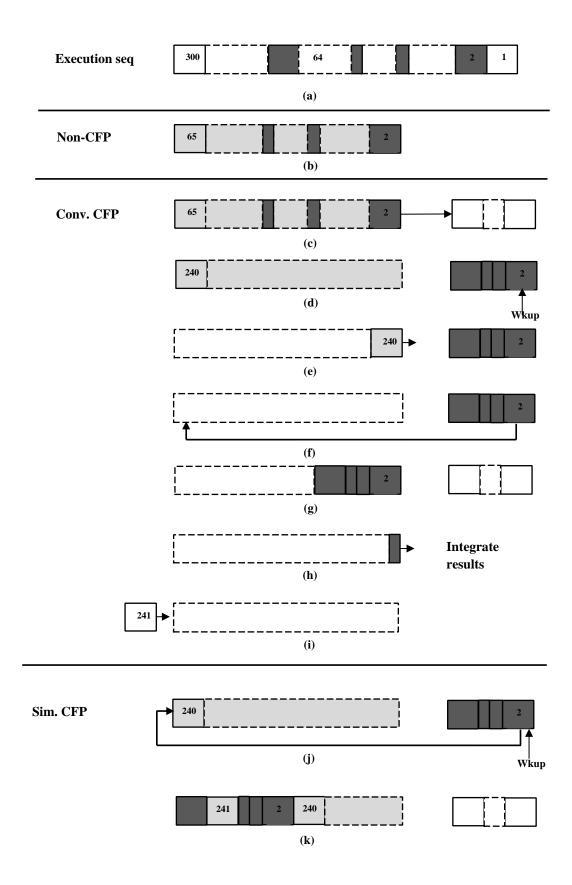

Figure 9(a) shows an execution sequence of instructions from *#1* to *#300*. Instruction *#2* misses the last level cache and will take a long time to execute. The cache miss dependents are shown as dark shaded boxes. All the following blocks represent the pipeline resources like reorder buffer entries and load store queue entries. Occupied pipeline resources are shown as shaded, while unoccupied resources are shown in white. The boxes on the right side show the low complexity slice buffer where load miss instructions and their dependents wait until the miss data arrives. The non-CFP ROB processor does not have a slice buffer.

Figure 9. Execution sequence demonstrating the pipeline flush limitation of conventional-CFP 30

We assume a 64 entry reorder buffer for this example. Figure 9(b) shows that the non-CFP ROB processor stalls after instruction #65 is brought into the pipeline because #2 cannot proceed forward until the cache miss data returns. Notice that even though all non-shaded instructions between #2 and #65 execute in the out-of-order processor, they still stay in the pipeline holding onto their resources because #2 is blocking them, and as a result the ILP that can be exploited by a non-CFP processor is limited.

Figures 9(c) - 9(i) show the working of a conventional-CFP processor. When the load miss instruction #2 is found to be blocking the pipeline, it is moved into the slice buffer as shown in Figure 9(c). Figure 9(d) shows that all miss-dependents or shaded instructions, including those beyond #64, move into the slice buffer. Though not explicitly shown in the figure, the miss-dependents also carry their ready input sources from miss-independent execution into the slice buffer. While the miss-dependents move into the slice buffer, CFP is able to process a lot more instructions compared to non-CFP ROB, indicated by the fact that CFP is able to take processing forward up to instruction #240 when the wakeup for #2 arrives as shown in the same Figure 9(d).

After the wakeup arrives, the front end of the conventional-CFP processor is stalled; so no more instructions after #240 are brought into the pipeline, indicated by the white slots in Figure 9(e). As shown in Figure 9(f), finally when the pipeline is drained, the slice instructions can be reintroduced into the pipeline. The shaded instructions are a self-contained slice and though separated in the original program as shown in the execution sequence of Figure 9(a), they can be executed together as a block in the second wave as shown in Figure 9(g).

When all dependents complete without exceptions or mis-predictions, the

31

results of independent and dependent execution are integrated as shown in Figure 9(h). Only after this, the next instruction from the execution sequence #241 gets a chance to enter the pipeline, as shown in Figure 9(i).

As we see from the example, the main disadvantage of conventional-CFP is the pipeline flush that separates the execution of independents and dependents leading to a lot of unused pipeline slots whenever the dependents are replayed from the slice buffer. The impact of this pipeline flush was not very pronounced when conventional-CFP was introduced because it was applied to only last level cache misses that went to DRAM. In present generation processors, with integrated memory controllers and large on-chip caches, applying CFP to only misses that go to DRAM will give less benefit, especially on CPU benchmarks. Targeting the other kind of misses, that is first level misses that hit higher on-chip caches, is also equally important. Although they do not incur as much delay as a miss to DRAM, they occur more frequently and consequently have the same impact on performance as a last level cache miss. Moreover, this allows designing processor cores with smaller instruction buffers to suit the L1 hit case.

However, conventional switch-on-event CFP cannot be applied to first level misses because the pipeline flush penalty will override the benefits of CFP execution. To overcome the limitation of conventional-CFP, in this dissertation, we propose to execute the independent and dependent instructions concurrently, similar to a simultaneous multithreading (SMT) architecture. We call this simultaneous-CFP (S-CFP) processor core architecture.

For the same working example, when the dependents block forward progress, like conventional-CFP, they are moved into the slice buffer as shown in Figure 9(c). But unlike conventional-CFP, when the wakeup arrives, the pipeline is not drained. The slice instructions are reissued while the independents are active in the pipeline as shown in Figure 9(j). Notice that the slice instructions execute as a separate thread, so they can be reintroduced into the pipeline, inter-mingled with the independents, as shown by the non-contiguous shaded instructions in Figure 9(k). The key impact of concurrent execution is that the empty or white slots are completely avoided with this approach. Avoiding the pipeline flush overhead allows CFP to be applied on first level misses as well for better performance as we will show in the results section.

# 2.2.4 Kilo Instruction Processors

Gonzalez et al. [15] proposed using virtual registers to shorten the lifetime of physical registers. Refer Section 2.3 for more details on virtual registers.

Kilo instruction processors [10] also used virtual renaming and ephemeral registers to do late allocation of physical registers. KILO scales the register file using a combination of virtual registers and reference counting. At rename, logical registers are mapped to virtual registers - a namespace larger than the set of physical registers. The virtual register name is then re-mapped to a physical register only when it needs a physical location – that is when the instruction produces a result after execution. KILO reference counts these virtual register names to determine when they can be reclaimed, and reclaims the underlying physical register at the same time. For the load or store queues, KILO cites various prior proposals, including those used by CFP, and states that any would be satisfactory.

Decoupled KILO-Instruction Processor (D-KIP) [40] improves the register management scheme of KILO by using two different processors – a Cache Processor for independents and a Memory Processor for dependents. In D-KIP, instructions start in the Cache Processor. The Cache Processor is a conventional out-of-order processor, except that miss-dependent instructions are forced out of its ROB after a certain number of cycles. As miss-dependent instructions leave the Cache Processor, they are placed into a FIFO queue which connects to an in-order Memory Processor. Miss-dependents capture their ready register input values as they exit the Cache Processor, so that the Memory Processor remains a self-contained slice. D-KIP maintains precise register state in the Cache Processor using checkpoints. D-KIP scales the load and store queues using hierarchy.

# 2.2.5 Flea-Flicker

Flea-Flicker [4][5] executes a program on two in-order back-end pipelines coupled by a queue. An advance pipeline executes independent instructions without stalling on long latency cache misses while deferring dependent instructions. A backup pipeline executes the instructions deferred in the advance pipeline and merges them with results stored in the queue from the advance pipeline. Flea-flicker executes instructions in an in-order pipeline, saves advanced instructions and results in its queue and merges results sequentially during backup pipeline execution.

# 2.2.6 iCFP and BOLT

iCFP [17] tolerates cache misses at all levels in the cache hierarchy, but uses an in-order pipeline, which is less suitable for the performance needs of conventional single-threaded applications.

BOLT [18] utilizes additional map tables in Simultaneous Multithreading architecture to re-rename L2 miss-dependent slice, combined with a program order slice and a unified physical register file that supports aggressive register reclamation. BOLT reuse of SMT hardware is to improve energy efficiency and performance.

#### 2.2.7 Sun Microsystems Rock

Sun Microsystems Rock is a single die multicore processor for high throughput computing. Rock uses Simultaneous Speculative Threading [7] to defer dependent instructions into a buffer, and executes the deferred instructions from the checkpoint after the miss data returns. The deferred instructions execution uses a simultaneous hardware thread and merges the results into the scout thread future file. Rock uses an inorder pipeline, similar to iCFP and is thus less suitable for the performance needs of single-threaded applications.

### 2.3 Simultaneous Multithreading

Simultaneous multithreading (SMT) [48][49] is a technique that allows multiple independent threads to issue multiple instructions each cycle to a superscalar processor's execution units. SMT benefits from multiple instruction issue of current superscalars and latency hiding ability of multithreading. SMT allows threads to share resources without context switching delays by having all thread register contexts active simultaneously. SMT also works around the limited thread instruction parallelism by having instructions from multiple independent threads in the scheduling window, providing plenty of opportunity to keep the superscalar execution units at full utilization. SMT can be implemented as an extension to a superscalar in a straightforward manner. Changes necessary to support SMT on a superscalar are:

- Multiple program counters and a fetch unit arbitration mechanism.

- Separate return address stack per thread.

- Separate retirement, branch mis-prediction, and exception recovery logic for each thread.

- A register alias table for each thread in the rename unit.

- Larger register file to support logical registers for all threads as well as additional registers for renaming.

Because dependencies between instructions are established at the rename stage, instructions from different threads can share the instruction buffers, the register file, execution units and read/write ports to the cache. The issue logic does not have to keep track to which thread an instruction belongs. Execution proceeds in a dataflow manner as usual. The primary impact is the enlarged size of the register file, especially for instruction sets which have a large number of logical registers. The enlarged register file may require an additional cycle in the pipeline to perform the read, and an additional cycle to write results, as suggested in [49].

Although SMT can be very useful in increasing throughput when running multiple programs, it is still limited in some respect. Sharing the cache hierarchy and the chip pin bandwidth among multiple programs limits the efficiency of these resources in comparison to running a single program. On the other hand, multithreading a single program, does not limit cache efficiency to the same degree, especially when instructions from the two threads lie very close to each other. Since this dissertation targets CFP on first level misses and majority of first level misses hit on-chip caches, the SMT threads comprise of closely lying instructions from the single program and usually benefit from constructive cache accesses.

# 2.4 Architectures with Virtual Register Renaming

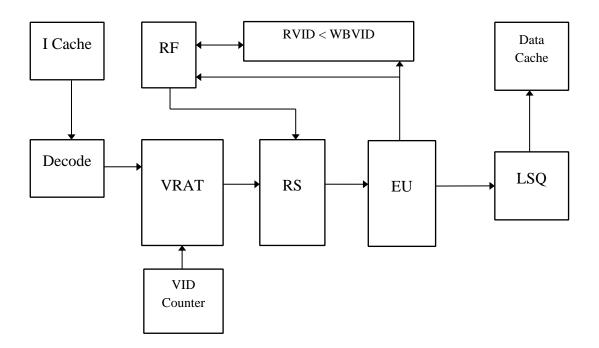

The mechanisms proposed in this dissertation to improve earlier CFP architectures benefit immensely from the concept of virtual register renaming. This section gives a brief account of prior work done on virtual registers.

# 2.4.1 Virtual Registers