## AMERICAN UNIVERSITY OF BEIRUT

# Verification of Software and Embedded Systems using AIG Solvers

by MOHAMAD ALI NOUREDDINE

A thesis submitted in partial fulfillment of the requirements for the degree of Masters in Engineering to the Department of Electrical and Computer Engineering of the Faculty of Engineering and Architecture at the American University of Beirut

> Beirut, Lebanon May 2014

## AMERICAN UNIVERSITY OF BEIRUT

## Verification of Software and Embedded Systems using AIG Solvers

by MOHAMAD ALI NOUREDDINE

Approved by:

Dr. Fadi Zaraket, Assistant Professor Electrical and Computer Engineering

Dr. Louay Bazzi, Associate Professor Electrical and Computer Engineering

Dr. Wassim Masri, Associate Professor Electrical and Computer Engineering

Date of thesis defense: May 8<sup>th</sup>, 2014

Advisor

Member of Committee

Member of Committee

## AMERICAN UNIVERSITY OF BEIRUT

# THESIS, DISSERTATION, PROJECT RELEASE FORM

| Student Name : | Noureddine          | Mohamad                   | Ali                |

|----------------|---------------------|---------------------------|--------------------|

|                | Last                | First                     | Middle             |

|                |                     |                           |                    |

|                |                     |                           |                    |

| Master's Thesi | s $\bigcirc$ Master | 's Project $\bigcirc$ Doc | toral Dissertation |

□ I authorize the American University of Beirut to: (a) reproduce hard or electronic copies of my thesis, dissertation, or project; (b) include such copies in the archives and digital repositories of the University; and (c) make freely available such copies to third parties for research or educational purposes.

✓ I authorize the American University of Beirut, three years after the date of submitting my thesis, dissertation, or project, to: (a) reproduce hard or electronic copies of it; (b) include such copies in the archives and digital repositories of the University; and (c) make freely available such copies to third parties for research or educational purposes.

Signature

Date

### Acknowledgments

Foremost, I would like to thank God for giving me the chance to continue my graduate studies at the American University of Beirut, and for allowing me to enjoy the support of all the wonderful people I have met during this journey. It is also through the divine guidance of the Quoran and the Holy prophet Muhammad and his family that I was able to keep faith throughout the hardships and obstacles that I have faced.

Imam Zainul Abideen (a.s.) says in his Treatise of Rights:

The right of the one who trains you through knowledge is magnifying him, respecting his sessions, listening well to him, and attending to him with devotion. You should not raise your voice toward him. You should never answer anyone who asks him about something, in order that he may be the one who answers. You should not speak to anyone in his session nor speak ill of anyone with him. If anyone ever speaks ill of him in your presence, you should defend him.

I am forever indebted to my thesis adviser, Fadi Zaraket, for the continuous guidance and help he provided me with during my period of graduate studies. His approach to logic and formal methods is what attracted me towards this field and kept me interested in it. It is with his encouragement and accurate advice that I was able to tackle the problems I faced in my research. I would also like to extend my gratitude to Fadi for the confidence he put in me and for allowing me to extend the work he started in his PhD.

I am also full of gratitude to my thesis committee members, Louay Bazzi and Wassim Masri, for their constructive comments and advice. I would also like to thank them for making my thesis an enjoyable and instructive experience. I would also like to thank Mohamad Jaber for the help that he provided me with in my work, especially for investing his time in a common research project, and for assisting me in finding an internship opportunity.

Furthermore, I could not have completed this stage of my academic life without the unconditional love, constant care and support, and prayer of my beloved fiancé Samah Karim. Thank you for being by my side and for listening to my constant nagging in the times where I faced obstacles in my research. I couldn't have imagined a better companion for me in my journey and my life.

Finally, key to my academic success is the support of my father, Ali, my mother, Sonia, and my brother, Houssein. I owe all of the goals I was able to reach in my life to their constant care and encouragement. I would also like to thank them for the huge faith that they had in me all along the way, which has pushed me to reach my production limits and beyond.

#### AN ABSTRACT OF THE THESIS OF

#### MOHAMAD ALI NOUREDDINE

for <u>Master of Engineering</u> Major: Electrical and Computer Engineering

Title: Verification of Software and Embedded Systems using AIG Solvers

It is critical for software and hardware developers to design correct and reliable systems. In particular, safety critical systems such as medical equipment, navigation control and targeting devices do not tolerate defects in their logical components. Static analysis techniques are used to check and prove correctness of logic components with respect to formal specifications. In particular, ABC is a model checker that takes an And-Inverter-Graph (AIG) circuit, a directed acyclic graph with two input AND gates, inverters and memory elements, reduces it using synthesis algorithms, and checks it for correctness using proof algorithms. Existing techniques transform software programs and embedded system design components into Conjunctive Normal Form (CNF) formulae and Symbolic Model Verifier (SMV) code, and use satisfiability (SAT) solvers and symbolic model checkers, respectively, to check their validity within a user specified finite domain. These techniques often fail to scale well with the increasing size of systems and with larger finite domains.

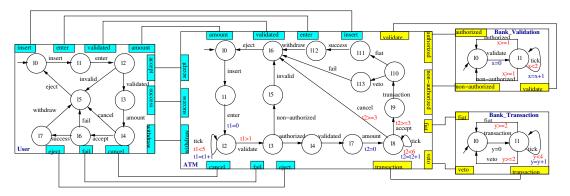

In this work, we explore the use of AIG solvers to address the verification of software and embedded systems subject to bounds on the data width of their variables.  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  translates imperative logic systems, written in a C-like language, into AIG.  $\mathcal{BIP}{I}$  translates an embedded system, written within the Behaviour-Interaction-Priority (BIP) framework, into AIG. Both methods use the ABC AIG solver to reduce the generated AIG circuits using sequential synthesis algorithms, and then check them for validity. The solver either (1) proves the specifications valid within the finite domain, (2) generates a counter example and reports it to the developer for debugging, or (3) reaches its computational bounds before making a decision. We evaluated  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  against a set of array and list manipulation algorithms, and various benchmarks obtained from the second competition on software verification (SV-Comp'13). Results show that  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  reaches bounds higher than those possible with the CBMC bounded model checker. It was also able to rank amongst the top three tools in the software verification competition. We also evaluated  $\mathcal{BIP}{I}$  against two benchmarks, an Automatic Teller Machine (ATM) system and the Quorum consensus protocol.  $\mathcal{BIP}{I}$  surpasses the NuSMV model checker on both designs.

# Contents

| Co            | onten             | ts                                         | vii            |

|---------------|-------------------|--------------------------------------------|----------------|

| $\mathbf{Li}$ | st of             | Figures                                    | ix             |

| $\mathbf{Li}$ | st of             | Tables                                     | x              |

| 1             | Intr              | oduction                                   | 1              |

|               | 1.1               | Advantages of sequential circuits          | 3              |

| 2             | Bac               | kground                                    | <b>5</b>       |

|               | 2.1               | Sequential circuits                        | 5              |

|               | 2.2               | The $CAIG$ component language              | 6              |

|               | 2.3               | ABC sequential solver                      | $\overline{7}$ |

|               |                   | 2.3.1 Structural Register Sweep (SRS)      | $\overline{7}$ |

|               |                   | 2.3.2 Signal Correspondence (Scorr)        | 8              |

|               |                   | 2.3.3 Rewriting                            | 8              |

|               |                   | 2.3.4 Retiming                             | 8              |

|               |                   | 2.3.5 Property Directed Reachability (Pdr) | 8              |

|               |                   | 2.3.6 Temporal Induction                   | 9              |

|               |                   | 2.3.7 Interpolation                        | 9              |

| 3             | $\{\mathcal{P}\}$ | $S{Q}$ : Imperative Programs to AIG        | 11             |

|               | 3.1               | Limitations of translation to CNF          | 13             |

|               | 3.2               | The $\mathcal{T}iny$ imperative language   | 14             |

|               | 3.3               | Translation to AIG                         | 15             |

|               |                   | 3.3.1 Preprocessing                        | 15             |

|               | 3.4               | Tranformation to $\mathcal{CAIG}$          | 20             |

|               | 3.5               | $\mathcal{CAIG}$ to AIG                    | 22             |

| <b>4</b>      | BIP               | ${\mathcal{I}}{\mathcal{I}}$ : BIP to AIG  | 26             |

|               | 4.1               | BIP - Behavior Interaction Priority        | 26             |

|               |                   | 4.1.1 Component-based Construction         | 27             |

|               | 4.2               | BIP to $CAIG$                              | <br>29         |

|               | 4.3               | Illustrative Example                       | 31             |

| <b>5</b> | Implementation                                                      | 36 |

|----------|---------------------------------------------------------------------|----|

|          | 5.1 $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$                     | 36 |

|          | 5.2 $\mathcal{BIP}\{\mathcal{I}\}$                                  |    |

| 6        | $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$ Results                 | 42 |

|          | 6.1 Searching: $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$ and CBMC | 42 |

|          | 6.2 Standard benchmarks                                             | 44 |

|          | 6.3 SV-COMP 2013 benchmarks                                         | 46 |

| 7        | $\mathcal{BIP}{I}$ Results                                          | 49 |

|          | 7.1 The ATM benchmark                                               | 49 |

|          | 7.2 The Quorum protocol                                             | 50 |

| 8        | Related work                                                        | 53 |

|          | 8.1 Verification of software programs                               | 53 |

|          | 8.2 Verification of embedded systems                                | 54 |

| 9        | Conclusion                                                          | 56 |

| Bi       | ibliography                                                         | 57 |

# List of Figures

| 2.1 | CAIG component language grammar                                                                                                                            | 7  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | (a) Array search program, and (b) equivalent array search program with                                                                                     |    |

|     | program counter                                                                                                                                            | 12 |

| 3.2 | The $\mathcal{T}iny$ imperative language $\ldots \ldots \ldots$ | 16 |

| 3.3 | Transformation function $\rho$ on function calls $\ldots \ldots \ldots \ldots \ldots \ldots$                                                               | 17 |

| 3.4 | Transformation function $\rho$ on universal quantifier                                                                                                     | 19 |

| 3.5 | Post processing of a $CAIG$ $C$                                                                                                                            | 23 |

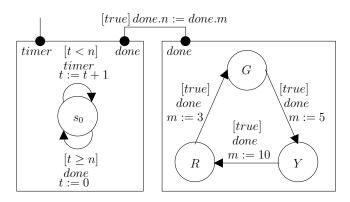

| 4.1 | Traffic light controller BIP system                                                                                                                        | 26 |

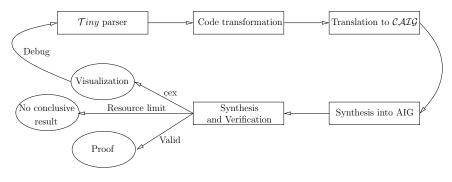

| 5.1 | Architecture of $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$                                                                                                | 36 |

| 5.2 | Example source code                                                                                                                                        |    |

| 5.3 | $\mathcal{BIP}{\mathcal{I}}$ 's command line options                                                                                                       | 41 |

| 6.1 | The linear search algorithm with pre and post conditions                                                                                                   | 43 |

| 6.2 | The binary search algorithm with pre and post conditions                                                                                                   |    |

| 7.1 | Modeling of ATM system in BIP                                                                                                                              | 49 |

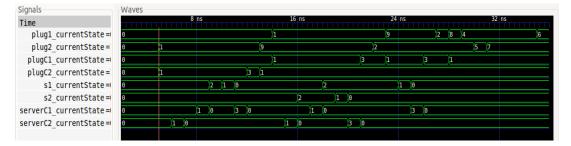

| 7.2 | Visualization of a counter example using Gtkwave                                                                                                           |    |

# List of Tables

| 2.1                                       | ABC algorithms                                                                                                                                        | 10       |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.1                                       | Sample of $\mathcal{BIP}{I}$ execution                                                                                                                | 32       |

| 5.1                                       | Summary of $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$ commands $\ldots \ldots \ldots$ | 40       |

| $\begin{array}{c} 6.2 \\ 6.3 \end{array}$ | $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}\$ and CBMC comparison                                                                                      | 46<br>47 |

|                                           | ATM results                                                                                                                                           |          |

# Chapter 1 Introduction

It is critical for software and hardware developers to design correct and reliable systems. In particular, safety critical systems such as medical equipment, navigation control and targeting devices do not tolerate defects in the their logical components. A logical defect might lead to severe consequences including loss of human life. A loss of precision due to a conversion from 64-bits into 16-bits of an integer value, caused the Ariane-5 missile to crash only 16 seconds after it has been launched. Additionally, a software bug in the control of a radiation therapy machine, "Therac-25", has lead to the death of six cancer patients between 1985 and 1987 [1].

In addition, information technology (IT) systems have made their way into several aspects of modern life. Smart phones, TVs, personal computers, laptops, banking, money transfer and e-shopping rely on IT systems. Logic defects in such systems can lead to loss of service, as well as other damages. Intel had to recall its faulty Pentium processors, that had a bug in the floating point unit, for a cost of 475 million US dollars [2].

Researchers introduced techniques to (1) accurately specify the requirements of logic components, (2) validate that the implementation of a logic component respects the specifications for a finite bounded domain, and (3) prove that a logic component respects its specifications for unbounded domains. *Dynamic analysis* techniques exercise the logical component for a given set of inputs, e.g. test cases, and check the results against a correctness predicate or an oracle [1]. Exhaustive testing is impossible in practical scenarios, because it involves exercising a practically infinite number of test cases [3].

Static analysis techniques are used to check and prove correctness of logic components with respect to formal specifications. Tools exist that synthesize, optimize, and check sequential circuits. ABC [4] is an industrial strength academic sequential synthesis and verification tool. It takes as input an And-Inverter-Graph (AIG) representation of a sequential circuit, reduces it using synthesis and reduction algorithms, and checks it for correctness using proof algorithms. An AIG is a directed acyclic graph with two input AND gates, inverters and memory elements. Since AND gates and inverters (i.e. NAND gates) are functionally complete, the restriction of logic gates to ANDs and inverters does not affect expressiveness.

Software systems are usually designed in high level programming languages

such as C, C++ and JAVA. Software verification tools such as CBMC [5] take as input software programs and check them for memory safety, array access safety, and user defined assertions (invariants). Given bounds on the unwinding depth of the loops, and on range of variables in the program, CBMC unfolds the program into a Boolean *Conjunctive Normal Form* (CNF) formula that asserts the specified properties. CBMC then uses Boolean *satisfiability* (SAT) solvers such as MiniSat [6] to check for correctness. CBMC verification tasks often fail to scale well with the increase in the size of the problem; specifically, with the loop unwinding bound and the complexity of the program.

Furthermore, in recent years, the application area of embedded systems has witnessed a large expansion, especially with the emergence of automotive electronics and mobile and control devices. Computations in embedded systems are subject to several physical and architectural constraints that render the separation between software and hardware design impractical [7]. The Behavior-Interaction-Priority (BIP) framework is a *Component-Based System* (CBS) design framework that uses a dedicated language and tool-set in order to support a rigorous and layered design flow for embedded systems. It allows to build complex systems by coordinating the behavior of a set of atomic components [8]. In order to check CBS, the BIP framework uses: (1) DFinder [9], a compositional and incremental verification tool-set, and (2) the NuSMV [10] model checker. However, DFinder does not handle data transfer between individual BIP components, and does not support checking for properties other than deadlock freedom. Additionally, for complex systems, NuSMV often suffers from the state space explosion problem [11], and fails to perform its verification tasks.

In this thesis, we present two techniques with supporting tools to address the verification of both software systems and CBSs: (1)  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  and (2)  $\mathcal{BIP}\{\mathcal{I}\}$ , respectively.  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  is a tool that takes an imperative program  $\mathcal{S}$  with a specification, a precondition and postcondition pair  $(\mathcal{P}, \mathcal{Q})$ , and checks whether  $\mathcal{S}$  satisfies the specification. This check is performed within a bound b on the domain of the program and specification variables  $(\mathcal{S} \models (\mathcal{P}, \mathcal{Q})|_b)$ ; i.e. when the bounded inputs of  $\mathcal{S}$  satisfy  $\mathcal{P}$ , the outputs of  $\mathcal{S}$  satisfy  $\mathcal{Q}$ . The program is written in a subset of C++ that includes integers, arrays, loops, and recursion, extended with a do\_together construct. The specification consists of a precondition  $\mathcal{P}$  and a postcondition  $\mathcal{Q}$ , both written in *first order logic* (FOL). Our method translates the problem  $\mathcal{S} \models (\mathcal{P}, \mathcal{Q})|_b$  into an equisatisfiable AIG, and passes the AIG to ABC for sequential synthesis and model checking. If successful, the check implies that the  $\mathcal{S}$  satisfies its specification pair  $(\mathcal{P}, \mathcal{Q})$ . Otherwise, it returns a counterexample and enables the developer to visualize it using the GtkWave [12] waveform viewer for debugging.

$\mathcal{BIP}{\mathcal{I}}$  is a tool that targets two design goals of the BIP framework: (1) verification and (2) code generation. Similarly to  ${\mathcal{P}}{\mathcal{S}}{\mathcal{Q}}$ , it takes an input BIP system with a set of optional specifications, and translates it in an equisatisfiable AIG. It then uses the ABC model checker to perform synthesis and verification. Additionally, unlike the BIP code generator used in [8] that uses a generic implementation of the BIP engine,  $\mathcal{BIP}{\mathcal{I}}$  generates an AIG system with a customized engine that is able to execute multiple atomic component transitions simultaneously.

#### **1.1** Advantages of sequential circuits

We formally define sequential circuits in Chapter 2; for now a sequential circuit can be viewed as a restricted C++ program, specifically a multi-threaded program in which all variables are either integers, whose range is statically bounded, or Boolean-valued, and dynamic allocation is forbidden [13].

There are two key advantages to compiling systems into sequential circuits:

- Advantage 1 Sequential encodings are much more succinct than pure combinational SAT formulae. They are imperative and state-holding while CNF formulas, for example, are declarative and state-free. For example, they can naturally represent the execution of quantifiers and loops without the need for unrolling them. Moreover, they can store and reuse intermediate results in local variables. In cases, SAT encoding algorithms produce a data structure that uses several orders of magnitude more memory to represent.

- Advantage 2 Casting the decision problem for a property of a system as an invariant check on a sequential circuit allows us to make use of a number of powerful automated analysis techniques that we discuss in Chapter 2 and that have no counterpart in CNF analysis.

$\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}\$  and  $\mathcal{BIP}\{\mathcal{I}\}\$  use ABC [4] to automatically check invariants in AIGs. ABC is a transformation-based verification (TBV) [14] framework that encompasses reduction and abstraction techniques such as retiming [15], redundancy removal [16, 17, 18, 19], logic rewriting [20], interpolation [21], and localization [22]. It operates on AIGs; Boolean netlists with memory elements, and iteratively and synergistically calls numerous transformation and abstraction algorithms. These algorithms simplify and decompose complex problems until they become tractable for decision techniques such as symbolic model checking, bounded model checking, induction, interpolation, circuit SAT solving, and target enlargement [23, 24, 25, 26, 27].

In this thesis we make the following contributions.

- We encode an imperative program S with a first order logic specification  $(\mathcal{P}, \mathcal{Q})$  into an AIG with an invariant that is stuck to *true* iff S satisfies  $\mathcal{Q}$  for all inputs that satisfy  $\mathcal{P}$  within a given bound on the range of the program variables.

- We use a program counter semantics to encode the S and  $(\mathcal{P}, \mathcal{Q})$  into an AIG. We use that to encode and compute a termination guarantee check within a bound on the number of iterations or recursive calls a program can make. We use the termination guarantee bound to prove run time efficiency of given algorithms.

- We encode a BIP system into an AIG with an invariant that is stuck to *true* iff the system is deadlock free, or satisfies a set of specifications. The generated AIG system will have its own customized engine that is able to execute multiple transitions simultaneously.

- We allow for simulation of the BIP system by generating a C++ code, while allowing for optional user control over the interactions to execute.

- We use the ABC sequential circuit verification framework to check the generated AIGs, and we check systems and programs that are orders of magnitude higher than those possible with the other techniques.

- We implement our methods in two tools:  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  and  $\mathcal{BIP}\{\mathcal{I}\}$ .

- We provide our tools and benchmarks online <sup>1</sup>.

The rest of this thesis is organized as follows. Chapter 2 gives an overview of the preliminary information needed throughout this thesis. Chapters 3 and 4 present the techniques used in  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  and  $\mathcal{BIP}\{\mathcal{I}\}$ , respectively. Chapter 5 highlights the main implementation details and gives a brief user manual for each of the two tools. We present our results in chapters 6 and 7. We discuss relevant related work in chapter 8 to finally conclude in chapter 9.

<sup>&</sup>lt;sup>1</sup>http://webfea.fea.aub.edu.lb/fadi/dkwk/doku.php?id=sa

# Chapter 2 Background

In this chapter, we present formalisms used throughout this thesis. A reader wellformed in logic verification and sequential circuits may wish to skip this section, using it only as a reference.

Let  $V = \{v_1, v_2, \dots, v_m\}$  be a set of scalar variables and  $A = \{a_1, a_2, \dots, a_n\}$  be a set of array variables.

**Definition 1** (terms). A *term* is either a variable  $v \in V$ , a constant  $c \in \mathbb{Z}$ , or an indexed array variable of the form a[t] which denotes the  $t^{th}$  element of a where  $a \in A$  and t is a term. Arithmetic expressions of the form  $-t, t_1 + t_2, t_1 - t_2, t_1 * t_2, t_1/t_2, t_1\%t_2$  are all terms where  $t, t_1, t_2$  are terms and -, +, \*, /, and % denote the substraction, addition, multiplication, division and remainder operations, respectively.

**Definition 2** (Boolean term). A constant from the set  $\mathbb{B} = \{true, false\}$  is a Boolean term. The expressions  $t_1 < t_2, t_1 \leq t_2, t_1 > t_2, t_1 \geq t_2, t_1 = t_2$  are all Boolean terms where  $t_1, t_2$  are terms and  $\langle \langle \langle \rangle \rangle \rangle$ , and == denote smaller, less than or equal, bigger than, bigger than or equal, and equal, respectively. The expressions  $b_1 \& \& b_2, b_1 \| \| b_2, !b_1, - \rangle$ , == are all Boolean terms where  $b_1, b_2$  are Boolean terms and  $\& \&, \| \|, !, - \rangle$ , and == denote logical conjunction, disjunction, negation, implication, and equivalence, respectively.

**Definition 3** (First order logic formula). A Boolean term is a *first order formula*. A quantified formula of the form Qq.b(q), where  $Q \in \{\forall, \exists\}$  is either a universal or existential quantifier, q is a quantified variable, and b(q) is a first order formula with q as a free variable.

#### 2.1 Sequential circuits

The ABC solver operates on an sequential circuit representation of a program.

**Definition 4** (Sequential circuit). A sequential circuit is a tuple ((V, E), G, O). The pair (V, E) represents a directed graph on vertices V and edges  $E \subseteq V \times V$  where E is a totally ordered relation. The function  $G: V \mapsto types$  maps vertices to types. There are three disjoint types: primary inputs, bit-registers (which we often simply refer to as

registers), and logical gates. Registers have designated *initial values*, as well as *next-state functions*. Gates describe logical functions such as the conjunction or disjunction of other vertices. A subset O of V is specified as the *primary outputs* of V. We will denote the set of primary input variables by I, and the set of bit-register variables by R.

**Definition 5** (Fanins). We define the direct *fanins* of a gate u to be  $\{v : (v, u) \in E\}$  the set of source vertices connected to u in E. We call the *support* of  $u \{v : (v \in I \lor v \in R) \land (v, u) \in *E\}$  all source vertices in R or I that are connected to u with \*E, the transitive closure of E.

The ABC solver reasons about And-Inverter-Graphs (AIG) which are acyclic sequential circuits with only AND gates and inverters. All AND gates are restricted to have 2 fanins. Since AND gates and inverters are functionally complete, this is not a limitation. For the sequential circuit to be syntactically well-formed, vertices in I should have no fanins, vertices in R should have 2 fanins (the next-state function and the initial-value function of that register) and gates should have two fanins. The initial-value functions of R shall have no registers in their support. All sequential circuits we consider will be well-formed.

**Definition 6** (State). A *state* is a Boolean valuation to vertices in *R*.

**Definition 7** (Trace). A *trace* is a mapping  $t : V \times \mathbb{N} \to \mathbb{B}$  that assigns a valuation to all vertices in V across time *steps* denoted as indexes from  $\mathbb{N}$ . The mapping must be consistent with E and G as follows. Term  $u_j$  denotes the source vertex of the j-th incoming edge to v, implying that  $(u_j, v) \in E$ . The value of gate v at time i in trace t is denoted by t(v, i).

$$t(v,i) = \begin{cases} s_v^i & : v \in I \text{ with sampled value } s_v^i \\ t(u_2,i-1) & : v \in R, i > 0, u_2 := \text{ next-state of } v \\ t(u_1,0) & : v \in R, i = 0, u_1 := \text{ initial-state of } v \\ G_v(t(u_1,i),...,t(u_n,i)) & : v \text{ is a combinational gate with function } G_v \end{cases}$$

The semantics of a sequential circuit are defined with respect to semantical traces. Given an input valuation sequence and an initial state, the resulting trace is a sequence of Boolean valuations to all vertices in V which is consistent with the Boolean functions at the gates. We will refer to the transition from one valuation to the next as a *step*. A node in the circuit is justifiable if there is an input sequence which when applied to an initial state will result in that node taking value true. A node in the circuit is valid if its negation is not justifiable. We will refer to targets and invariants in the circuit; these are simply vertices in the circuit whose justifiability and validity is of interest respectively.

#### 2.2 The CAIG component language

```

1 component: decl wiredef init 'while(true)' '{' next '}'

2 type: bool | int | bool '['NUM']' | int '['NUM']'

3 declaration: wire type ID ';' | type ID ';'

4

5 decl: declaration+

6 wiredef: (target = expr ';')*

7

8 init: '@do_together' '{' (target = expr ';')* '}'

9 next: '@do_together' '{' (target = expr ';')* '}'

10 target: ID | ID '['expr']'

11 expr: expr? expr : expr

```

Figure 2.1: CAIG component language grammar

The grammar in Figure 2.1 describes CAIG, a high level imperative language that describes a sequential circuit. An CAIG program starts with a list of declarations of wire, register, and array variables. Wires are defined in a list of assignment statements in the wiredef block. Each wire can be the target at most one assignment statement. If a wire is not assigned, then it is left as a free input to the circuit.

The init list of statements assigns initial values for the register variables. All assignment statements within the init block execute simultaneously as indicated with the do\_together keyword. Similarly, the next list of statements updates the values of the register variables.

Each assignment statement has a left hand side target term which is either a variable or an access operator to an array element. The right hand side of an assignment is a combinational expression that is either a term (from Definition 1) or a ternary choice expression. The ternary choice (a?b:c) returns b if a is true and c otherwise.

#### 2.3 ABC sequential solver

ABC is an open source sequential circuit solver that operates on a sequential circuit in AIG format and checks the satisfiability of a designated output gate therein. ABC applies several reduction and abstraction techniques to simplify and decompose the problem into smaller problems. It then calls decision techniques to decide the simplified problems. In what follows we discuss some of the techniques that are briefly listed in Table 2.1.

#### 2.3.1 Structural Register Sweep (SRS)

SRS detects registers that are stuck-at-constant and eliminates them from a given sequential AIG circuit. The technique starts by zeroing up all initial values of registers in the circuit. It then uses the ternary simulation algorithm in order to detect stuckat-constant registers. The algorithm starts from the initial values of the registers and simulates the circuit using x values for the circuit's primary inputs. The simulation algorithm stops when a new ternary state is equal to a previously computed ternary state. In this case, any register having the same constant value at each reachable ternary state will be declared to be stuck-at-constant and thus eliminated. The structural sweeping algorithm stop when no further reduction in the number of registers is possible [28].

#### 2.3.2 Signal Correspondence (Scorr)

Scorr uses k-step induction in order to detect and merge sets of classes of sequentiallyequivalent nodes [28]. The base case for this algorithm is that the equivalence between the classes holds for the first k frames, and the inductive case is that given the base case, starting from any state, the equivalence holds in the  $(k + 1)^{st}$  state. Key to the signal correspondence algorithm is the way the candidate equivalences are assumed for the base case. Abc implements speculative reduction, originally presented in [35], which merges, but does not remove, any node of an equivalence class onto its representative, in each of the first k time frames. Instead of removing the merged node, a constraint is added to assert that the node and its representative are equal. This technique is claimed to decrease the number of constraints added to the SAT solved for induction.

#### 2.3.3 Rewriting

Rewriting aims at finding nodes in a Directed Acyclic Graph (DAG) where by replacing subgraphs rooted at these nodes by pre-computed subgraphs can introduce important reductions in the DAG size, while keeping the functionality of these nodes intact. The algorithm traverses the DAG in depth-first post-order and gives a score for each root node. The score represents the number of nodes that would result from performing a rewrite at this node. If a rewrite exists such that the size of the DAG is decreased, such a rewrite is performed and scores are recomputed accordingly. Rewriting has been proposed initially in [29], targeted for Reduced Boolean Circuits (RBC); it was later implemented and improved for ABC in [30].

#### 2.3.4 Retiming

Retiming a sequential circuit is a standard technique used in sequential synthesis, aiming at the relocation of the registers in the circuit in order to optimize some of the circuit characteristics. Retiming can either targets the minimization of the delay in the circuit, or the minimization of the number of registers given a delay constraint, or the unconstrained minimization of the number of registers in the circuit. It does so while keeping the output functionality of the circuit intact [31]

#### 2.3.5 Property Directed Reachability (Pdr)

The Pdr algorithm aims at proving that no violating state is reachable from the initial state of a given AIG network. It maintains a trace representing a list of overapproximations of the states reachable from the initial state, along with a set of *proofobligations*, which can be a set of bad states or a set of states from which a bad state is reachable. Given the trace and the set of obligations, the Pdr algorithm manipulates them and keeps on adding facts to the trace until either an inductive invariant is reached and the property is proved, or a counter example is found (a bad is state is proven to be reachable). The algorithm was originally developed by Aaron Bradley in [36, 37] and was later improved by Een et. al in [34].

#### 2.3.6 Temporal Induction

Temporal induction carries an inductive proof of the property over the time steps of a sequential circuit. Similar to a standard inductive proof, it consists of a base case and an inductive hypothesis. These steps are typically expressed as SAT problems to be solved by traditional SAT solvers. k-step induction strengthens simple temporal inductive proofs by assuming that the property holds for the first k time steps (states), i.e. a longer base case needs to be proven [32]. Since the target is to prove unsatisfiability (proving that the negation of the property is unsatisfiable), if the base case is satisfiable, a counter-example is returned. Otherwise, the induction step is checked by assuming that the property holds for all the states except the last one (the (k + 1)'th state) [38].

#### 2.3.7 Interpolation

Given an unsatisfiable formula  $A \wedge B$ , an interpolant I is a formula such that  $A \implies I$ ,  $I \wedge B$  is unsatisfiable and I contains only common variables to A and B. Given a system M, a property p and a bound k, interpolation based verification starts by attempting bounded model checking (BMC) with the bound k. If a counter-example is found, the algorithm returns. Otherwise, it partitions the problem into a prefix *pre* and a suffix suf, such that the problem is the conjunction of the two. Then the interpolant I of *pre* and suf is computed, it represents an over-approximation of the set of states reachable in one step from the initial state of the algorithm. If I contains no new states, a fixpoint is reached and the property is proved. Otherwise, the algorithm reiterates and replaces the initial states with new states added by I [33].

| Table 2.1: $l$ | Example | ABC | techniques |

|----------------|---------|-----|------------|

|----------------|---------|-----|------------|

| Technique           | Description                                    | ABC command |

|---------------------|------------------------------------------------|-------------|

| Balancing           | Balancing reduces the number of AIG levels     | balance     |

|                     | by applying associativity transformations [4]  |             |

| Structural Register | SRS reduces the number of registers in the     | scl -l      |

| Sweep (SRS)         | circuit by eliminating stuck-at-constant reg-  |             |

|                     | isters [28]                                    |             |

| Signal Correspon-   | Scorr computes a set of classes of             | ssweep      |

| dence (Scorr)       | sequentially-equivalent nodes using $k$ -step  |             |

|                     | induction [28]                                 |             |

| Rewriting           | AIG rewriting iteratively selects and replaces | rewrite     |

|                     | rooted AIG subgraphs with smaller pre-         |             |

|                     | computed subgraphs in order to reduce the      |             |

|                     | size of the AIG [29]                           |             |

| Refactoring         | AIG refactoring is a variation of AIG rewrit-  | refactor    |

|                     | ing that uses a heuristic algorithm to com-    |             |

|                     | pute one large cut for each AIG node, then     |             |

|                     | replaces the structure of these cuts with a    |             |

|                     | factored form if an improvement is observ-     |             |

|                     | able [30]                                      |             |

| Retiming            | Retiming aims at manipulating registers over   | retime      |

|                     | combinational nodes in a given logic network,  |             |

|                     | while maintaining the output functionality     |             |

|                     | and logic structure [31]                       |             |

| Temporal Induc-     | Temporal induction uses SAT solvers to         | ind         |

| tion                | carry simple and k-step induction proofs over  |             |

| T . 1               | the time steps of the sequential circuit [32]  |             |

| Interpolation       | Interpolation-based algorithms aim at find-    | int         |

|                     | ing interpolants in order to derive an over-   |             |

|                     | approximation of the reachable states of       |             |

|                     | the AIG network with respect to the prop-      |             |

|                     | erty [33]                                      |             |

| Property Directed   | Pdr tries to prove that there is no transi-    | pdr         |

| Reachability (Pdr)  | tion from an initial state of the AIG to a bad |             |

|                     | state [34]                                     |             |

# Chapter 3 $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$ : Imperative Programs to AIG

$\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}\$  targets the verification of imperative programs annotated with precondition and postcondition specifications. An imperative program is a sequence of instructions that describes in full details the steps that the execution unit must take to accurately implement the required functionality. In order to verify that a program accurately implements its functionality, the developer provides a set of formal specifications in the form of a precondition-postcondition pair. A precondition is a FOL formula over the the program's inputs that specifies which combination of inputs are acceptable; i.e. under which inputs the program is expected to work. A postcondition is a FOL formula over the program's inputs and outputs that defines the program's expected output. The postcondition relates the program's outputs to its inputs [39].

Given a program S, a precondition and postcondition pair  $(\mathcal{P}, \mathcal{Q})$ , and a bound b on the domain of S and its variables,  $\{\mathcal{P}\}S\{\mathcal{Q}\}$  checks whether S satisfies its specifications  $(S \models (\mathcal{P}, \mathcal{Q})|_b)$ ; i.e. when the bounded inputs of S satisfy  $\mathcal{P}$ , the outputs of S must necessarily satisfy  $\mathcal{Q}$ .  $\{\mathcal{P}\}S\{\mathcal{Q}\}$  accepts programs written an imperative language,  $\mathcal{T}iny$ , a subset of C++ extended with support for FOL and a block synchronization construct, the do\_together block. The tool then translates the problem  $(S \models (\mathcal{P}, \mathcal{Q})|_b)$  into an equisatisfiable AIG using a program counter encoding. The generated AIG has a single output o that is set to 1 iff S violates its specifications. The tool then uses the ABC sequential AIG model checker [4] to check that o is never set to 1. If the check is successful, S satisfies its specifications. Otherwise,  $\{\mathcal{P}\}S\{\mathcal{Q}\}$  returns the violating trace (i.e. the counterexample) to the user for debugging of S.

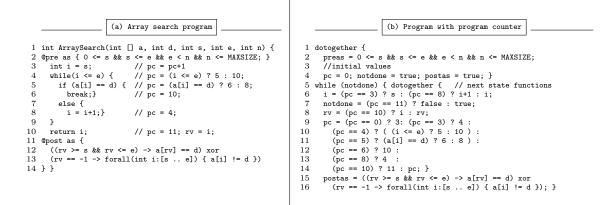

The Array search program in Figure 3.1(a) takes as input an array a, a start index s, an end index e, a data value d, and the number of elements in the array n. It is annotated with a specification consisting of a precondition and a postcondition. The precondition states that the start s and end e indices are within array bounds and that the array size n is within the bound on array sizes. The postcondition states that if rvis valid between s and e inclusive, then a[rv] must be equal to d, otherwise, rv must be invalid (-1) and all entries in a between s and e inclusive are not equal to d.

Figure 3.1(b) shows an equivalent encoding of the array search program using a program counter execution model. The equivalent program introduces Boolean

Figure 3.1: (a) Array search program, and (b) equivalent array search program with program counter

variables **preas**, **postas**, and **notdone** to encode the precondition, the postcondition, and the running state of the program, respectively. The equivalent program also introduces a program counter variable **pc** which encodes the control flow of the program as indicated in the comments of Figure 3.1(a). The **rv** variable denotes the return value of the original program.

The notdone variable is initialized to *true*, and pc program counter is initialized to the first executable line of the program 3. Once pc reaches the last executable line of the program 13, the program terminates and thus notdone becomes *false*. Assignment statements are grouped by target variables, and encoded into conditional assignment statements that depend on the value of pc. For example, the iterator i is assigned to s when pc is 3, incremented when pc is 8, and remains the same otherwise.

The program in Figure 3.1(b) is semantically equivalent to the original program in Figure 3.1(a). Furthermore, the assignment statements on Lines 1 and 3 assign initial values to the target variables. The assignment statements inside the while loop (Lines 5 to 13) compute the next state value of each of the target variables of the program.

Our method translates the program in Figure 3.1(b) to a sequential circuit where an iteration of the while loop is equivalent to a single time step in the sequential circuit. The method represents each Boolean variable with one register, and each scalar variable with a finite vector (bit-vector) of registers with initial value and next state functions. The initial state functions of the vector of registers corresponding to a variable are connected to a vector of gates that represents the right hand side initial value assignment statement of the variable. For example, pc ranges from 0 to 11 and can be encoded using 4 registers.

Program variables that are not initialized in the code are considered input variables and the methods connects their initial value functions to free primary inputs. The method connects the next state functions of register vectors corresponding to program variables to gates that represent the right hand side of the next state assignment. The conditional, arithmetic, and Boolean operations in the right hand side expressions are encoded as combinational logic circuits in the usual manner.

Our method takes the resulting sequential circuit, designates a gate therein that represents  $preas \land done \rightarrow postas$  as the output gate, passes the circuit to ABC, and checks for the validity of the designated gate. The ABC solver returns a counterexample a = [000], s = 0, e = 1, n = 3, d = 1, rv = 2 where d is not in a, and the return value is e + 1, while the postcondition requires an invalid index (-1).

The provided counter example can be used to fix the program. A possible fix is to replace Line 6 with return i;, and Line 10 with return -1;. Our method takes the fixed program, transforms it into a sequential circuit, and passes it to ABC which validates the correctness of the program modulo the finite size of the variable vectors using symbolic model checking.

#### **3.1** Limitations of translation to CNF

Existing tools such as CBMC [5] check for pointer safety, within bound array access and user defined assertions in C programs. Given a C program and a bound on the range of variables, CBMC unwinds the program's loops and recursive functions, and unfolds the program into a Boolean (CNF) formula that asserts the specified properties. It then uses SAT methods and tools such as MiniSat [6] to check the CNF formula for counter examples.

Recent advances in SAT enabled tools like the Alloy Analyzer [40] and CBMC to check designs of real systems. However, these designs often need to be partial, leaving out important functionality aspects of the systems, to enable the analysis to complete. Moreover, the analysis is typically bound to relatively small limits, e.g., fewer than 7 nodes in a tree structure with the Alloy Analyzer.

There are three limiting aspects of translating high-level programs to SAT.

- **Disadvantage 1** The translation to CNF depends on the bounds; a small increase in the bound on variable ranges can cause a large increase in the size of the translated CNF formula due to unwinding loop and recursion structures in programs, or eliminating quantifiers in declarative first order logic.

- **Disadvantage 2** The SAT solver is restricted to using optimizations, such as symmetry breaking [41] and observability don't cares (ODC) [42], that apply at the level of CNF formulas. However these optimizations usually aim at increasing the speed of the solver and often result in larger formulas as they add literals and clauses to the CNF formula to encode symmetry and ODC optimizations [43]. Often times when the analyzer successfully generates a large CNF formula, the underlying solver requires intractable resources.

- **Disadvantage 3** Often times the CNF formula generated needs to be regenerated with higher bounds in case the unwinding bounds were not large enough for the loops to complete as is the case with CBMC. Note that multiple bounds exist and they need not be all increased during one iteration.

To extend the applicability of static analysis to a wider class of programs as well as to check more sophisticated specifications and gain more confidence in the results, we need to scale the analysis to significantly larger bounds; limits on the range of design and program variables.

The work in [44] takes a declarative formula  $\phi$  in first order logic (FOL) with transitive closure and a bound on the universe of discourse and translates it to a sequential circuit expressed in VHDL. It then passes the sequential circuit to a sequential circuit solver and decides the validity of  $\phi$  within the bound. It scales to bounds larger than what is possible with Kodkod [45] which translates  $\phi$  into a propositional Boolean formula in conjunctive normal form (CNF) and checks its validity with a Boolean satisfiability solver.

The work in [46] translates an imperative C program, with an assertion statement therein, and a bound on the input size, into a sequential circuit expressed in VHDL. It then passes the sequential circuit to a sequential circuit solver and decides the validity of the assertion within the bound. It scales to bounds larger than what is possible with CBMC[47] which translates the program with a bound on the input size and the number of loop iterations into a propositional Boolean formula in conjunctive normal form (CNF) and checks for correctness using a Boolean satisfiability solver.

Our method extends the work in [44, 46] in that

- it supports function calls including recursion, and requires a bound on recursion depth only if the recursive function uses local variables,

- it enables a termination guarantee check within a bound on execution time, it then uses the execution time bound with bounded model checking to decide correctness,

- it directly translates the program into bit level representation using *and inverted* graphs (AIG) instead of the VHDL representation that requires a VHDL compiler to be translated into bit level,

- it uses ABC [4], an open source sequential circuit solver, instead of SixthSense [48] an IBM internal sequential circuit solver,

- and it is an open source tool available online <sup>1</sup>.

#### 3.2 The Tiny imperative language

The grammar in Figure 3.2 describes  $\mathcal{T}iny$ ,  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$ 's imperative input language. It is composed of a subset of the C++ programming language, extended with first order logic support and some special constructs. A **program** is a list of declarations and statements. Variables can be declared to be of two kinds: (1) wires and (2) registers. Wires are non-memory elements used to monitor the values of different variables or terms in the program, at every instance in the program's execution. Once assigned to a term, wires will reflect the value of the term at every point in the program. On the contrary, register variables are memory elements that only change value once they are the target of an assignment statement executed at a specific program point. The value

<sup>&</sup>lt;sup>1</sup>http://webfea.fea.aub.edu.lb/fadi/dkwk/doku.php?id=sa

of a register variable is memorized between two different assignment statements. In what follows, we refer by wires to wire variables, and by variables to register variables.

A variable can either be single or an array. Arrays can be declared to have a constant predefined size, or can be left free to have the maximum number of elements to be determined by  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$ 's runtime engine. Similarly, wires can either be singular or arrays.  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  currently support one dimensional and two dimensional arrays. Given a two dimensional array a of size n by m where n and m are constants, the tool transforms a into a single dimensional array a' of size  $n \times m$ , and translates all array accesses a[i][j] into accesses of the form  $a'[i \times (n \times m) + j]$ .

Statements can be assignment statements, control statements or synchronization statements. Assignment statements modify the state of program by assigning new values to select program variables. Control statements are used to modify the control state of the program by selecting the next program location, possibly begin dictated by the value of a certain term.  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}\$  supports the **if-then-else** selection control statement and the **while** loop control statement. Synchronization statements start with the **dotogether** modifier, and are used to enforce the execution of a list of data-independent assignment or selection statements at the same program point (equivalently, at the same clock cycle).

Additionally,  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  provides support for *function definitions* and *function calls*. Defining and calling a function is done in the same manner as in a regular C++ program, with the exception that **return** statements must always be present at the end of a function's body.  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  allows also allows the declaration of recursive functions. Expressions in  $\mathcal{T}iny$  extend the definition of terms presented in Definition 1 of Chapter 2 with the addition of allowing terms to also be function calls, as depicted by the notation **term\_with\_function\_call** on line 31 of Figure 3.2.

$\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}\$  extends the subset of C++ above with support for FOL specifications, written in the form of *pre-condition*, *post-condition* pairs. FOL expressions are Boolean expressions that can be Boolean terms or function calls, or *quantified expressions*. A quantified expression is either universally (forall) or existentially (exists) quantified.

#### **3.3** Translation to AIG

Given an imperative program S written in the  $\mathcal{T}iny$  language, and annotated with a FOL precondition postcondition specification pair  $(\mathcal{P}, \mathcal{Q})$ ,  $\{\mathcal{P}\}S\{\mathcal{Q}\}$  transforms the tuple  $(S, (\mathcal{P}, \mathcal{Q}))$  into an  $\mathcal{CAIG}$  program S'. The tool then synthesizes S' into an equisatisfiable AIG C having a single output representing the formula  $\neg (\mathcal{P} \land S \implies \mathcal{Q})$ . The tool then uses the ABC AIG solver to verify the validity of  $\neg o$  and thus prove that S satisfies its specification pair  $(\mathcal{P}, \mathcal{Q})$  if successful. If the validity check fails, the tool returns a counterexample to be used by the developer for debugging.

#### 3.3.1 Preprocessing

$\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}\$  first starts by transforming  $\mathcal{S}$  into an intermediate program  $\mathcal{S}' = \rho(\mathcal{S})$  where  $\rho$  is a code transformation function that simplifies function calls, recursive functions

```

1 program: block+

2 block: (declaration | statement)

3 statement: assignment_statement | conditional_statement |

loop_statement | sync_statement

6 // declarations

7 declaration: variable_declaration | function_declaration | property_declaration

% variable_declaration: modifier? type id ('[' num ']' ('[' num ']')?)?

('=' term)?

9

10 function_declaration: type id '(' argument_list? ')'

'{' block* return_statement '}'

11

12

13 // statements

14 assignment_statement: target '=' expression ';'

15 sync_statement: '@dotogether' '{' (assignment_statement | conditional_statement)+ '}'

16 conditional_statement: 'if' '(' expression ')' '{' block '}'

'else' '{' block+ '}'

17

18 loop_statement: 'while' '(' expression ')'

'{' block+ '}'

19

20 return_statement: 'return' expression ';'

21

22 // properties

23 property_declaration: precondition | postcondition

24 precondition: '@pre' id '{' property+ '}'

25 postcondition: '@post' id '{' property+ '}'

26 property: expression | quantified_property

27 quantified_property: ('forall'|'exists') '(' range ')'

'{' property+ ';' '}'

28

29

30 // expressions

31 expression: term_with_function_call

32 function call: id ((' call_arguments? ')'

33 call_argument: id (',' id)*

34

35 argument_list: variable_declaration (',' variable_declaration)*

36 modifier: 'wire' | 'const'

37 specifier: 'int' | 'bool'

38 target: id | target '[' expression ']'

39 range: id '[' expression '...' expression ']'

```

Figure 3.2: The  $\mathcal{T}iny$  imperative language

and properties.

**Function calls.**  $\rho$  does not inline functions; instead, it uses a program counter mechanism to avoid inlining and reuse the same code and thus the same AIG after synthesis. Key to that is the transformation of function class as follows. Let  $f(args_f)$  by a call to function declaration  $f_d(args_{f_d}$  where  $args_f$  is a list of expressions passed as arguments to f, and  $args_{f_d}$  is the list of arguments declared in  $f_d$ . Let  $ret(f_d)$  be

Figure 3.3: Transformation function  $\rho$  on function calls

the return variable of  $f_d$ , and  $args_f(i)$  and  $args_{f_d}(i)$  be the i'th argument passed to fand declared in  $f_d$ , respectively, for  $0 \le i \le |args_f|$ .

Consider the assignment statement  $s = (target := f(args_f))$  where target is the target of the assignment as defined in line 38 of Figure 3.2. The transformation function  $\rho(s)$  is defined as follows:

$$\rho(s) = \begin{cases} \left( \begin{array}{c} |args_f| (args_{f_d}(i) := args_f(i)) \\ call\_func(f_d) ; (target := ret(f_d)) \end{array} \right); \\ (3.1)$$

The ; operator represents an ordering of the statements, where  $s_1$ ;  $s_2$  means that  $s_1$  executes before (or possibly at the same time as)  $s_2$ . Intuitively,  $\rho$  copies the arguments passed to the call f onto the arguments declared in the function declaration  $f_d$ . It then adds the call\_func( $f_d$ ) statement, a special statement that redirects the control of the program to the starting point of  $f_d$ 's body. It finally assigns that *target* of s to the return variable of the function  $f_d$ .

**Recursive functions.** Let  $f_d(args_{f_d})$  be a recursive function with arguments  $args_{f_d}$ , and let  $f(args_f)$  be a recursive call to  $f_d$ , i.e. a call to  $f_d$  from inside the body of  $f_d$ . Using  $\rho$ ,  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  emulates recursion by (1) adding a stack pointer variable  $sp_{f_d}$  that maintains the recursive depth of the current function call, and (2) increasing the dimensionality of all arguments and local variable of  $f_d$  by 1. In other words, variables become arrays and arrays become two dimensional arrays. Subsequently, all assignments and references to arguments or local variables of  $f_d$  are replaced by array access terms indexed by the current value of  $sp_{f_d}$ . The recursion depth (i.e.  $sp_{f_d}$ ) is incremented before each recursive call f and decremented once it returns. Consider the assignment statement  $s = (target := f(args_f))$  where target is the target of the assignment as defined in line 38 of Figure 3.2, and f is a recursive call to  $f_d$ . The transformation function  $\rho(s)$  is then defined as follows:

$$\rho(s) = \begin{cases}

\left( \begin{array}{l} |args_{f}| (args_{f_d}(i)[sp_{f_d}+1] := args_f(i)) \\

(sp_{f_d} := sp_{f_d}+1); call\_func(f_d); (sp_{f_d} := sp_{f_d}-1) \\

(target := ret(f_d)[sp_{f_d}+1]);

\end{array} \right) (3.2)$$

Note that arguments of  $f_d$  to be assigned are indexed by the future value of the recursion stack depth pointer (i.e.  $sp_{f_d} + 1$ ) before the the pointer is incremented. The same is applied to the return variable of  $f_d$  after the pointer has been decremented.

Additionally, consider the assignment statement  $s = (target := f(args_f))$ where f is a non-recursive call to  $f_d$ ,  $sp_{f_d}$  is guaranteed to have a value of 0 and the transformation function  $\rho(s)$  is defined as:

$$\rho(s) = \begin{cases}

\left( \begin{array}{c} |args_f| \\ i=0 \end{array} (args_{f_d}(i)[0] := args_f(i)) \right); \\

call_func(f_d); (target := ret(f_d)[0]); \\

\end{array} (3.3)$$

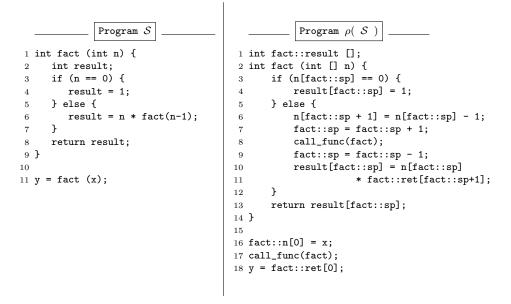

Figure 3.3 shows an example of applying the transformation function  $\rho$  onto a program containing a recursive function call fact(n) that computes the factorial of an integer n. The argument n of fact and the local variable result are transformed into the arrays fact::n and fact::result. fact::sp is the recursive stack pointer variable added by  $\rho$  for the function fact. Local references to n are result are replaced by the sequence access terms fact::n[fact::sp] and result[fact::sp].

Lines 6-11 of  $\rho(S)$  in Figure 3.3 show the result of applying *rho* on the recursive function call fact(n-1) on line 6 of the program S. The next value of the argument n is assigned to the current value of n decremented by 1, as shown in the statement fact::n[fact::sp + 1] = fact::n[fact::sp] - 1. The stack pointer variable is then incremented before adding the function call statement call\_func(fact) that gives the control to the body of the function fact. Once the function call returns, the stack pointer variable is decremented, and any reference to the return variable of fact is replaced by an array access term to the next value of the stack pointer (fact::sp + 1). Lines 16-18 of S' shows the result of applying  $\rho$  to a non-recursive call to fact, in which the arguments and return variable of fact are replaced by array access terms indexed by 0.

**Quantifiers.** Consider the assignment statement  $s = (target := Q(i : [t_1 ... t_2]) \{\mathcal{B}\})$ where *target* is the target variable of the assignment, Q is either 'forall' or 'exists', i is a quantified variable,  $t_1$  and  $t_2$  are terms representing the range of i, and  $\mathcal{B}$  is a Boolean FOL formula.  $\rho(s)$  is defined as follows:

$$\rho(s) = \begin{cases}

(Q_r := true); (i := t_1); \\

while(i <= t_2) \{ \rho(Q_r := Q_r (\&\& or ||) \mathcal{B}); (i := i + 1) \}; \\

(target := Q_r)

\end{cases}$$

(3.4)

Figure 3.4: Transformation function  $\rho$  on universal quantifier

For the quantified expression  $(Q(i : [t_1 \dots t_2]) \{\mathcal{B}\})$ ,  $\rho$  adds a Boolean return variable  $Q_r$  that is initialized to *true* and holds the value of the expression. Then  $\rho$  transforms the expression into a while loop that iterates over all possible values of i, and assigns the return variable  $Q_r$  to its current value conjuncted or disjuncted with the value of  $\mathcal{B}$ ). The type of the operation performed is determined by the nature of the quantifier; conjunction for the universal quantifier ('forall') and disjunction for the existensial quantifier ('exists').  $\rho$  finally adds the actual assignment statement of target as  $target := Q_r$ . Note that  $\rho$  is also applied to the update assignment to the variable  $Q_r$  in order to handle the cases where  $\mathcal{B}$  is also quantified or it contains a function call.

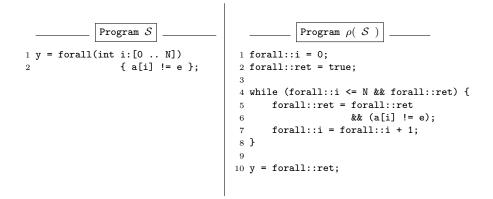

Figure 3.4 shows an example of applying the transformation function  $\rho$  on a program S containing an assignment of the variable y to a universal quantifier. Note that we added the expression forall::ret to the condition of the while loop in order to allow for early exit of the loop. Additionally, in the case the bounds on the quantified variable are constants, we optimize the transformation by unrolling the loop into a single large Boolean expression.

**Pre/Post conditions.** Consider the  $\mathcal{T}iny$  precondition and postcondition declarations @*pre*  $\mathcal{P}$  { $\mathcal{B}$ } and @*post*  $\mathcal{Q}$  { $\mathcal{F}$ } where  $\mathcal{B}$  and  $\mathcal{F}$  are Boolean expressions. For brevity, we refer by  $\mathcal{P}$  and  $\mathcal{Q}$  to the precondition and postcondition delcarations, respectively. The transformation function  $\rho$  is defined as follows:

$$\rho(\mathcal{P}) = \rho\left(x_{\mathcal{P}} := \mathcal{B}\right) \tag{3.5}$$

$$\rho(\mathcal{Q}) = \rho\left(x_{\mathcal{Q}} := \mathcal{F}\right); assert(x_{\mathcal{P}} \implies x_{\mathcal{Q}}) \tag{3.6}$$

$\rho$  creates for each declaration a Boolean variable that is used to hold its value across the program's execution.  $\rho$  then replaces the precondition declaration  $\mathcal{P}$  by a statement that assign its created variable  $x_{\mathcal{P}}$  to its declared FOL formula  $\mathcal{B}$ . Similarly,  $\rho$ replaces the postcondition declaration  $\mathcal{Q}$  by the statement  $x_{\mathcal{Q}} := \mathcal{F}$ . In order to resolve quantification or function calls in  $\mathcal{B}$  and  $\mathcal{F}$ , we also apply  $\rho$  to the created statements.

Additionally,  $\rho$  adds an assertion statement  $assert(x_{\mathcal{P}} \implies x_{\mathcal{Q}})$  after the postcondition assignment statement. This assertion statement will not be evaluated,

instead it used the help  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}\$  determine the outputs to pass to the ABC AIG solver for verification.

All statements and expressions in S that are not mentioned in this Section are kept unchanged by the transformation function  $\rho$ .

#### **3.4** Tranformation to CAIG

After preprocessing,  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  transforms the program  $\mathcal{S}' = \rho(\mathcal{S})$  into an equisatisfiable  $\mathcal{CAIG}$  program  $\mathcal{C}$ . Synthesizing an AIG from  $\mathcal{C}$  is then a direct translation of variables into bit registers and building their next state function according to the next block definition in  $\mathcal{C}$ .  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  uses program counter semantics to translate  $\mathcal{S}'$  into  $\mathcal{C}$ . The program counter is used to ensure the correct sequencing of assignments in the program; i.e. to provide the concept of time.

Our method assigns a unique *label* for each statement in the program S'. Let s be any statement in S', and let  $s_a, s_i, s_w$ , and  $f_d$  be an assignment statement, a conditional statement, a loop statement and a function declaration in S', respectively. Additionally, let e be an array access expression, and let  $call(f_d)$  be an added call\_func statement that calls the function declaration  $f_d$ . Our method defines the following functions:

- label(s): The unique label identifying the statement s

- next(s): The label of the statement that directly follows s in the program order.

- condition( $s_i$ ): The Boolean condition of the selection statement  $s_i$ .

- then  $(s_i)$ : The label of the first statement in the *then* code block of  $s_i$ .

- $else(s_i)$ : The label of the first statement in the *else* code block of  $s_i$ .

- condition  $(s_w)$ : The Boolean condition of the loo statement  $s_w$ .

- body  $(s_w)$ : The label of the first statement in the body of the  $s_w$ .

- last  $(s_w)$ : The last statement in the body of the loop  $s_w$ .

- target( $s_a$ ): The target variable of the assignment  $s_a$ .

- expression( $s_a$ : The expression to be assigned to the target of  $s_a$ .

- body  $(f_d)$ : The label of the first statement in the body of the function  $f_d$ .

- return  $(call(f_d))$ : The label of the statement to which the function call statement should return after calling  $f_d$ .

- base(e): The array which the expression e is indexing.

- index(e): The index at which the base of the expression e is indexed.

Algorithm 1 shows the procedure used in  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  to translate a preprocessed  $\mathcal{T}iny$  program  $\mathcal{S}'$  with a set of variables V and an initial entry statement, into an  $\mathcal{CAIG}$  program  $\mathcal{C}$ , to be used for the synthesis of the equisatisfiable AIG. Intuitively, the wire declarations, variable definitions and wire definitions are directly moved from  $\mathcal{S}'$  to their corresponding blocks in  $\mathcal{C}$ . Additionally, in order to model time,  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  adds a new scalar variable to the program  $\mathcal{S}'$ , the *program counter* pc. This variable is key to avoid inlining functions and unrolling loops. It is used to ensure the proper sequencing of the statements of  $\mathcal{S}'$ ; the current value of the pc variable defines which statement is to be execute. For example, reassigning the value of pc to the starting point of a loop's body allows  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  to make use of the same code block (thus the same AIG) to execute a single loop infinitely many times.

The algorithm starts by building the initialization list of C. It assigns the program counter variable pc to the label of the entry statement of S'. Then for each variable  $v \in V$  that is used before being assigned (i.e. used with an undefined value), it assigns v to a set of free inputs (AIG primary inputs) who's values are to be set by the ABC AIG solver. Note that since variables can be initialized at different points in the program (and not necessarily at the starting point of the algorithm), we delay their initialization step into the **next** block, where these variables will get their initial value at the appropriate **pc** value.

Subsequently, the algorithm moves to building the **next** state block of C. For each variable  $v \in V$ , and for each assignment statement s such that target(s) = v, the next state of v will be expression(s) iff pc == label(s). If at a given statement label, v is not being assigned, it retains its current value. For example, consider the following assignment statements for v:

```

1 (11): x = 1;

2 (12): x = 3;

3 (13): x = 5;

```

The algorithm builds the next state function of x as the following statement

```

1 x = (pc == 11)? 1 : (pc == 12)? 3 : (pc == 13)? 5 : x;

```

After traversing all of S's variables, the algorithm then builds the next state assignment for the program counter. At a given statement s, the default behavior of the pc is to move from the current label label(s) to the label of the statement that directly follows s, i.e. next(s). Only control statements such as conditional statements, loop statements, function call statements and return statements are allowed to alter the default behavior of pc.

Conditional statements alter the value of the program counter based on the evaluation of their conditional expression. Consider a conditional statement s and let e = condition(s). When pc is at label(s), its next value is either the label of the first statement in then then branch of s if e evaluates to true, or to the first statement in the else branch of s otherwise. Therefore at label(s), the next state of the pc is defined as (e)? then(s) : else(s).

Similarly, loop statements move the program counter into their body when their conditional expression evaluates to true, and to their next statement once it is *false*. Consider a loop statement *s* and let e = condition(s). At label(s), the next state

of pc is defined as (e)? body(s) : next(s). Note that according to the  $\mathcal{T}iny$ , the loop statement block is considered as a single statement, and thus the next statement to follow s would be the first statement outside its body, i.e. its exit point. Additionally, for the last statement in the body of the loop, its next statement is defined as the loop statement itself. This ensure that once the pc reaches that last statement in the loop, it once again evaluates its condition in order to determine whether to exit or stay in the loop.

Finally, function call statements and return statements redirect the program counter into the body of the function and to the first statement after the call, respectively. Note that for a non-recursive function, there is at most one active function call at a time, therefore it is easy to track the label at which the program counter should return to. For a recursive function, we maintain a stack of function calls and redirect the control to statement after the call that is on top of the stack.

#### Post-processing

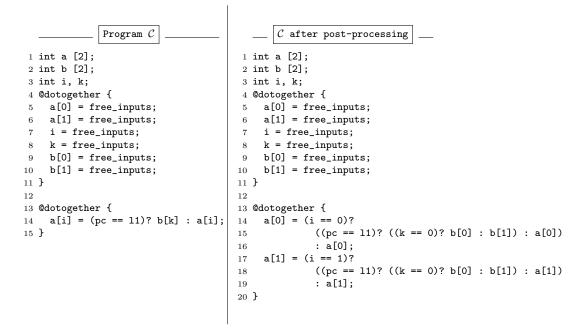

After constructing the CAIG program C,  $\{\mathcal{P}\}S\{\mathcal{Q}\}$  employs a last post-processing step to resolve array accessing. Given an array access expression a[i] where a is an array and i is an index, resolving this access expression is to transform it into an array access where the index is constant. An array access expression with a constant index is handled as a regular register variable in C.

The first part of algorithm 2 shows the post processing of a reference to an array access expression e. The algorithm pushes the variable index i outside of the array access by creating a set of checks for the value of i at each possible index of the array a, and returning the appropriate array element accordingly.

The second part of algorithm 2 shows the post processing of statement s where target(s) is an array access of the form a[i]. Since this assignment statement can be to any of the elements of the array a, as dictated by the value of i, the algorithm creates an assignment statement for each possible element of a. This ensure that only the correct element get assigned to the value of expression(e) by creating a check for i at each possible index of the array.

Figure 3.5 shows an CAIG program C that contains array access assignments and references. Post-processing transforms the assignment statement on line 14 of the program C into assignment statements over all the elements of the array a, with added checks on the value of the index i. Also post-processing replaces the expression b[k] in the right hand side of the assignment statements with the expression  $(k == 0)? \ b[0] :$ b[1]. This expression checks on the value of k for all possible indices to the array b and returns the corresponding element.

#### 3.5 CAIG to AIG

Given a bound b on the bit width of variables,  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}\$  synthesizes an AIG by a direct translation of a  $\mathcal{CAIG}$  program  $\mathcal{C}$  into a sequential circuit. The synthesis proceeds as follows. Scalar register variables and array elements are translated into vectors of b bits registers, while Boolean variables and array elements are directly mapped onto one bit

Figure 3.5: Post processing of a CAIG C

registers. The init block of  $\mathcal{C}$  is used to determine the initial value of the instantiated registers.

The next block of C infers the next state functions for all registers in the AIG, including the program counter. For each variable, we translate the expression of its next state function into a hierarchy of multiplexers that reflect the ternary choice expressions in C's assignment expressions.

Finally,  $\{\mathcal{P}\}\mathcal{S}\{\mathcal{Q}\}$  builds the primary output of the AIG as the negation of the assertion statement introduced in the pre-processing step. Given a precondition  $\mathcal{P}$  and a postcondition  $\mathcal{Q}$ , the primary output o will be  $\neg(x_{\mathcal{P}} \implies x_{\mathcal{Q}})$  where  $x_{\mathcal{P}}$  and  $x_{\mathcal{Q}}$  are the precondition and postcondition variables introduced in the pre-processing step.

Algorithm 1 T iny to CAIG transformation algorithm

```

1: Input: \mathcal{T}iny program \mathcal{S}', entry_statement

2: Output: CAIG program C

3:

4: // build the initialization list

5: init_list []

6: for all v \in V do

if used_before_assigned(v) then

7:

init_list.insert ("v = free_inputs")

8:

end if

9:

10: end for